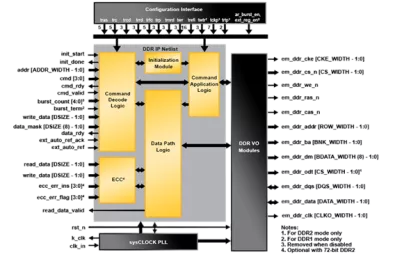

DDR SDRAM Controller IP

Filter

Compare

180

IP

from

23

vendors

(1

-

10)

-

SDRAM DDR Controller

- Dolphin Technology offers high performance DDR4/3/2 SDRAM and LPDDR5/4x/4/3/2 SDRAM Memory Controller IP across a broad range of process technologies.

-

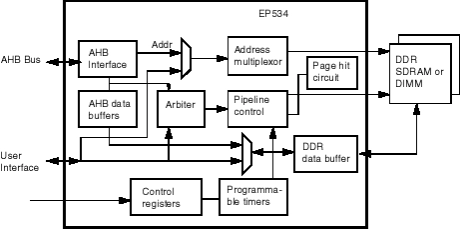

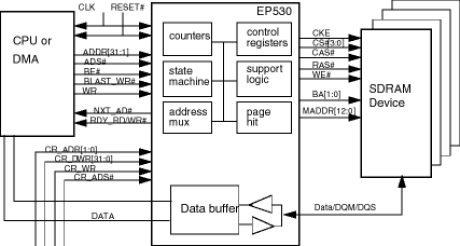

AMBA AHB Bus to DDR SDRAM Controller

- External pin reduction by transferring 2 bits of data per pin.

- Supports multiple external SDRAM banks.

- Automatic refresh generation with programmable refresh intervals.

- Self-refresh mode to reduce system power consumption.

- Standard delay cells or user provided DLL for DQ and DQS alignment.

-

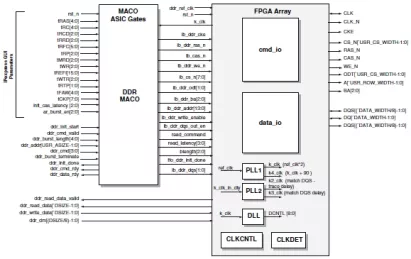

DDR SDRAM Controller - Pipelined for ispXPGA and ORCA4

- Performance of Greater than 100MHz (200 DDR)

- Interfaces to JEDEC Standard DDR SDRAMs

- Supports DDR SDRAM Data Widths of 16, 32 and 64 Bits

- Supports up to 8 External Memory Banks

-

DDR SDRAM Controller - Non-Pipelined

- Performance of Greater than 133MHz (266 DDR)

- Interfaces to JEDEC Standard DDR SDRAMs

- Supports DDR SDRAM Data Widths of 16, 32 and 64 bits

- Supports up to 8 External Memory Banks

-

DDR SDRAM Controller - Pipelined

- Interfaces to industry standard DDR SDRAM devices and modules

- High-performance DDR 400/333/266/200/133 operation for LatticeECP3, LatticeECP2/M, LatticeECP2/MS and LatticeSC/M devices; DDR 333/266/200/133 operation for LatticeECP/EC devices; and DDR 266/200/133 operation for LatticeXP devices

- Programmable burst lengths of 2, 4 or 8 for DDR

- Programmable CAS latency of 2 or 3 cycles for DDR

-

DDR SDRAM Controller

- Supports industry standard Double Data Rate (DDR) SDRAM.

- Designed for ASIC and FPGA implementations in various system environments.

- Programmable memory size and data width.

- Supports industrial standard 64Mbit, 128Mbit and 256Mbit DDR SDRAMs.

-

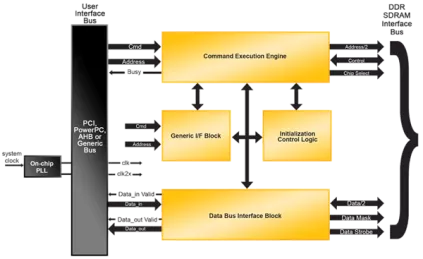

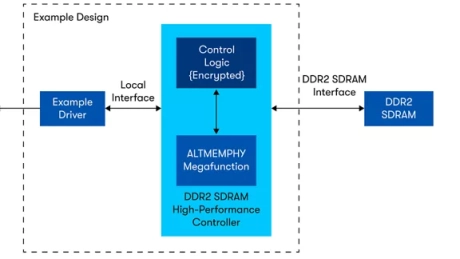

DDR and DDR2 SDRAM Controller with ALTMEMPHY Intel® FPGA IP

- The DDR and DDR2 SDRAM Controller with ALTMEMPHY Intel FPGA Intellectual Property (IP) provides simplified interfaces to industry-standard DDR SDRAM and DDR2 SDRAM

- The DDR and DDR2 SDRAM Controller with ALTMEMPHY Intel FPGA IP core work in conjunction with the ALTMEMPHY physical interface IP function

- The controllers offer a half-rate interface and a full-rate interface to the customer application logic

- For exact device support, please refer to the user guide.

-

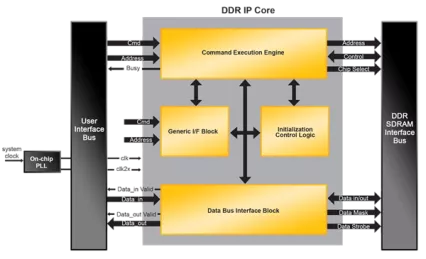

DDR and DDR2 SDRAM Controller Intel® FPGA IP Core

- The DDR and DDR2 SDRAM controllers handle the complex aspects of using DDR and DDR2 SDRAM—initializing the memory devices, managing SDRAM banks, and keeping the devices refreshed at appropriate intervals

- The controllers translate read-and-write requests from the local interface into all the necessary SDRAM command signals.

-

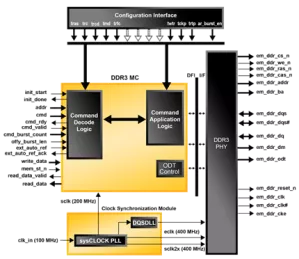

DDR3 SDRAM Controller

- Support for all LatticeECP3 “EA” devices

- Interfaces to Industry Standard DDR3 SDRAM components and modules compliant with JESD79-3, DDR3 SDRAM Standard

- Interfaces to DDR3 SDRAM at speeds up to 400 MHz / 800 Mbps in -8 speed grade devices

- Supports memory data path widths of -8, -16, -24, -32, -40, -48, -56, -64 and -72 bits

-