ColdFire IP

Filter

Compare

10

IP

from

2

vendors

(1

-

10)

-

ColdFire V2 Core with AMBA peripherals connected in a subsytem

- Building upon the 68K foundation, ColdFire offers RISC performance with industry-leading code density and a rich set of connectivity peripherals.

- By supporting variable-length instructions (16-, 32- or 48-bits long), the ColdFire Architecture enables higher code density than traditional 32- and 64-bit RISC machines.

- More efficient use of on-chip memory reduces bus bandwidth and external memory requirements, resulting in lower system cost.

-

ColdFire V4 Core with industry proven platform peripherals

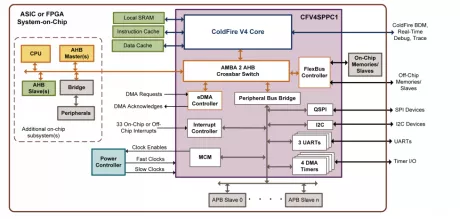

- The ColdFire V4 Core & Standard Product Platform (SPP) C1 (CFV4SPPC1) combines the ColdFire V4 Core with industry proven platform peripherals to form a complete high performance micro-controller subsystem supported by a vast ecosystem of development tools and runtime software.

-

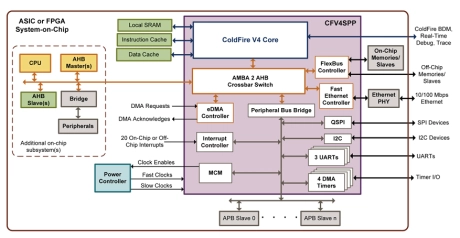

ColdFire V4 Core & Standard Product Platform

- The ColdFire V4 Core & Standard Product Platform (CFV4SPP) combines the ColdFire V4 Core with industry-proven platform peripherals to form a complete high-performance micro-controller subsystem supported by a vast ecosystem of development tools and runtime software.

-

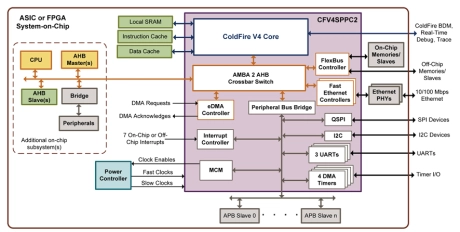

ColdFire V4 Core & Standard Product Platform (SPP) C2

- The ColdFire V4 Core & Standard Product Platform (SPP) C2 (CFV4SPPC2) combines the ColdFire V4 Core with industry proven platform peripherals to form a complete high performance micro-controller subsystem supported by a vast ecosystem of development tools and runtime software.

-

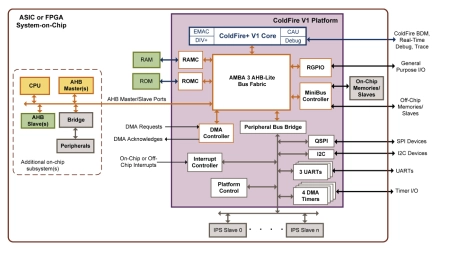

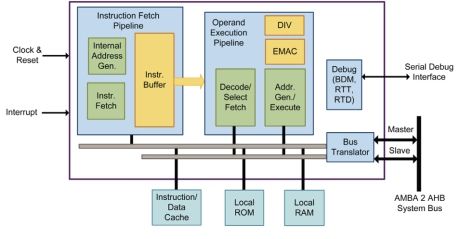

ColdFire V1 core with AMBA peripherals connected in a subsystem

- The ColdFire® V1 Platform (CFV1P) is a fully configurable micro controller subsystem built from the same ColdFire V1 processor IP that is implemented in ColdFire+ family devices from Freescale Semiconductor.

- The ColdFire V1 Platform extends the core processor platform used in Freescale’s MCF51Qx and MCF51Jx devices to include a set of production-proven peripheral modules, each of which can be included in or excluded from your ColdFire V1 Platform implementation depending on your system requirements.

-

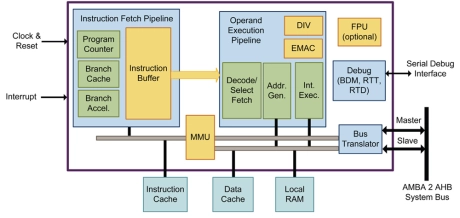

ColdFire V4 Processor delivering 500 DMIPS of performance

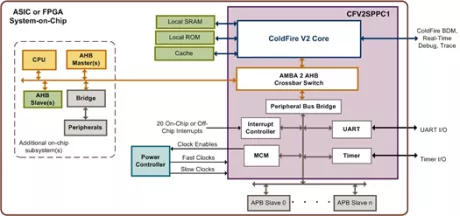

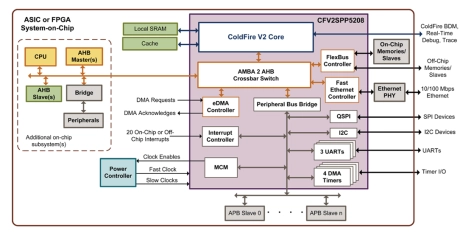

- The ColdFire V2 Core & Standard Product Platform (CFV2SPPC1) combines the ColdFire V2 Core with industry-proven platform peripherals to form a complete low-cost, low-power microcontroller subsystem supported by a vast ecosystem of development tools and runtime software.

- The CFV2SPPC1 is the same ColdFire V2 processor core and platform/peripheral IP implemented in NXP MCF5208 devices.

-

ColdFire V2 Core with single Fast Ethernet and AMBA peripherals connected in a subsytem

- Multi-AHB crossbar switch (AXBS) connects multiple masters with various slave IP blocks

- External Bus Interface for glueless connection to external memory devices

- 10/100 Fast Ethernet Controller (FEC) with direct memory access (DMA)

- Queued serial peripheral interface (QSPI)

-

ColdFire V1 core with EMAC, Divider and Cryptograhic unit

- The synthesizable 32-bit RISC ColdFire V1 Core (CFV1CORE) is the smallest and lowest power processor in the ColdFire family, using as few as 19K gates.

- The CFV1CORE small size and 32 bit performance make it ideal for a wide variety of consumer, healthcare, and other embedded systems applications.

-

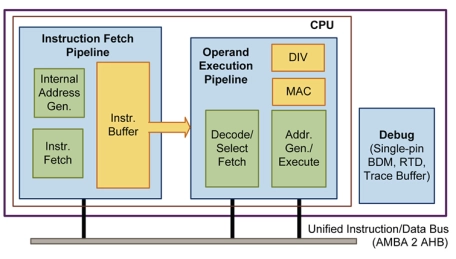

ColdFire V2 IP Core low-gate count, high performance ColdFire architecture

- Variable-length RISC, clock-multiplied core

- 166-MHz in typical 130-nm process

- Independent, decoupled pipelines: 2-stage instruction fetch pipeline (IFP); 2-stage operand execution pipeline (OEP); FIFO instruction buffer is the decoupling mechanism

- 16 user-accessible, 32-bit general purpose registers (GPRs)

-

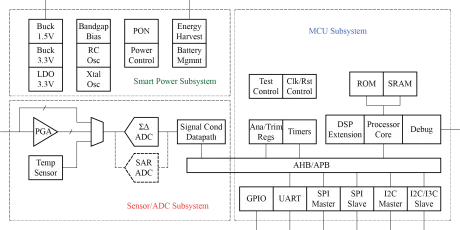

Intelligent Sensor and Power Management Design Platform

- Smart Power Subsystem

- Sensor AFE

- MCU Subsystem