Alphawave Semi IP

Filter

Compare

986

IP

from

86

vendors

(1

-

10)

-

Software tool for the automatic building of Power Management Unit (PMU)

- PowerStudio is an innovative software d to speed up the architecture, design and integration of complex, automotive-grade on-chip Power Management Units (PMU).

- It combines in a single tool a versatile solution for power network exploration with a unique capability to generate pre-verified RTL and UPF files of the power network.

-

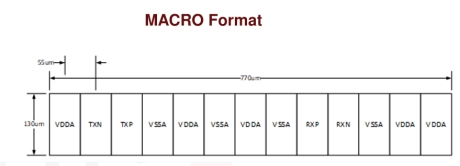

Specialed 20V Analog I/O in TSMC 55nm

- A TSMC 55nm LP Specialized 20V Analog I/O in Standard Low Voltage CMOS

- This silicon-proven TSMC 55nm LP 20V ESD cell is a high-voltage electrostatic discharge (ESD) protection solution specifically engineered forlow-power and high-performance applications.

- This ESD cellis designed to safeguard high- voltage interfaces commonly found in analog, mixed-signal, RF, and power management ICs, where protection against electrostatic discharge events is critical for long-term reliability.

-

ESD Solutions for Multi-Gigabit SerDes in TSMC 28nm

- A Wirebond and FlipChip compatible <80fF ESD Solutions for Multi-Gigabit SerDes Applications.

- This silicon-proven TSMC 28nm Digital I/O Library delivers a low-capacitance, high-reliability interface solution optimized for advanced semiconductor applications.

- Featuring low-capacitance LVDS differential pairs (<250fF per pin) at 0.8V, this library ensures superior signal integrity for high-speed applications.

-

UCIe based 8-bit 48-Gsps Transceiver (ADC/DAC/PLL/UCIe)

- 48-Gsps peak sample rate

- 8 bit resolution

- UCIe SP (16x lanes at 16Gbps) with streaming controller

-

UCIe based 12-bit 12-Gsps Transceiver (ADC/DAC/PLL/UCIe)

- 12-Gsps peak sample rate

- 12 bit resolution (programmable)

- UCIe SP (16x lanes at 16Gbps) with streaming controller

-

Fully-coherent RISC-V Tensor Unit

- The bulk of computations in Large Language Models (LLMs) is in fully-connected layers that can be efficiently implemented as matrix multiplication.

- The Tensor Unit provides hardware specifically tailored to matrix multiplication workloads, resulting in a huge performance boost for AI without a big power consumption.

-

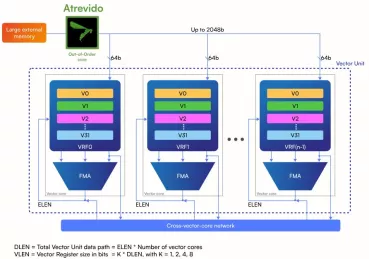

Fully-custom RISC-V Vector Unit

- A Vector Unit is composed of several "Vector Cores", roughly equivalent to a GPU Core, that perform multiple calculations in parallel.

- Each Vector Core has arithmetic units capable of performing addition, subtraction, fused multiply-add, division, square root, and logic operations.

-

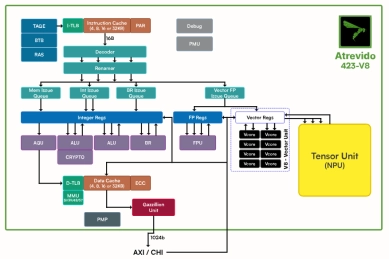

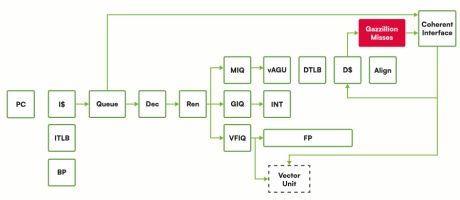

64-bit Out-of-Order RISC-V Customisable IP Core

- Ready for the most demanding workloads, Atrevido supports large memory capacities with its 64-bit native data path. With its complete MMU support, Atrevido is also Linux-ready, including multiprocessing.

-

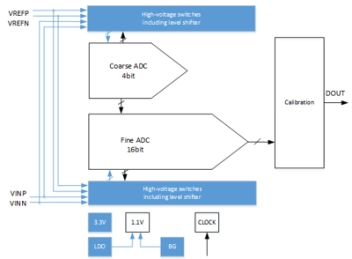

12-bit/16-bit SAR ADC

- 12 bits 100Msps SAR ADC on 28nm process;

- 12 bits 25Msps SAR ADC and Pipeline ADC above 100Msps on 40/55nm process;

- 16 bits 2/1Msps SAR ADC on 40/55nm process;

-

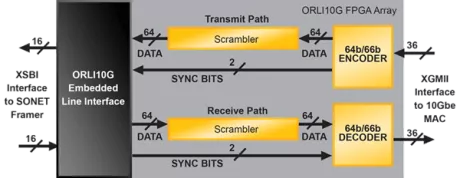

10Gb Ethernet PCS

- Complete 10Gb Ethernet Physical Coding Sublayer (PCS) Solution Based on the ORCA 10 Gbits/s Line Interface (ORLI10G) FPSC, Enabling Flexible10GbE LAN/WAN Application Solutions.

- IP Targeted to the ORLI10G Programmable Array Section Implements Functionality Conforming to IEEE Standard 802.3ae, Including:

- ORCA Bitstream Format Allows Direct Downloading and Turnkey Functionality.

- ModelSim Simulation Models and Test Benches Available for Free Evaluation.