AMBA CHI IP

Filter

Compare

126

IP

from

38

vendors

(1

-

10)

-

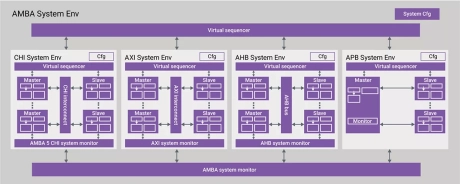

Verification IP for Arm AMBA CHI Protocol

- AMBA 5 CHI-A/B/C/D/E/F/G

- Request node, secondary node agents and monitor

- Complete port-level checks

- Supports all interface types

-

Simulation VIP for AMBA CHI

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Generates constrained-random bus traffic with predefined error injection

- Callbacks access at multiple queue points for scoreboarding and data manipulation

- Provides comprehensive checking and coverage model

-

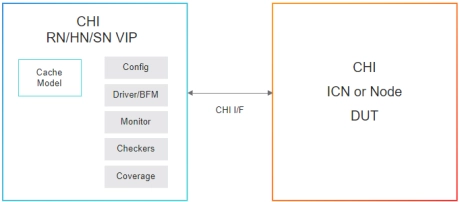

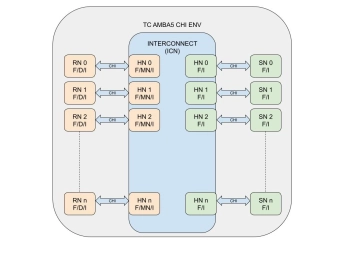

AMBA 5 CHI Verification IP

- VIP is Compliant with the latest ARM™ AMBA5 CHI.

- Support any type of network topology like Crossbar, Ring, Mesh, etc…

- Support for all types of AMBA5 CHI Nodes:

- Requester (RN-F, RN-D, RN-I)

- Home (HN-F, HN-I)

- Subordinate (SN-F, SN-I)

- Requester (RN-F, RN-D, RN-I)

-

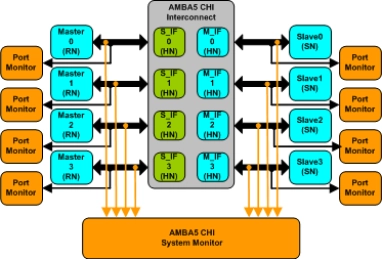

AMBA 5 CHI Verification IP

- Compliant with the latest ARM AMBA 5 CHI specification (CHI-D).

- Supports CHI Master, Slave, Interconnect, Monitor and Checker.

- Support for Protocol, Network and Link layer communication, including flow control mechanisms across RN2HN and HN2SN links.

- Supports all CHI protocol node types:

-

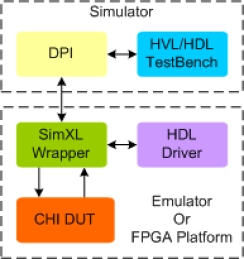

AMBA 5 CHI Synthesizable Transactor

- Compliant with the latest ARM AMBA 5 CHI specification (CHI-B).

- Supports CHI Master, Slave, Interconnect.

- Support for Protocol, Network and Link layer communication, including flow control mechanisms across RN2HN and HN2SN links.

- Supports all CHI protocol node types:

-

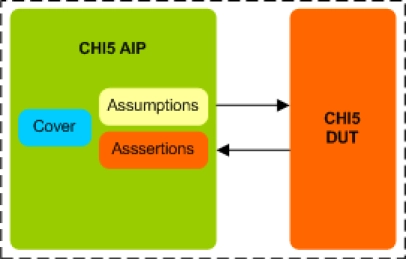

AMBA 5 CHI Assertion IP

- Specification Compliance

- Compliant with the latest ARM AMBA 5 CHI specification.

- Supports all ARM AMBA 5 CHI data widths.

- Supports for Protocol, Network and Link layer communication, including flow control mechanisms across RN2HN and HN2SN links.

-

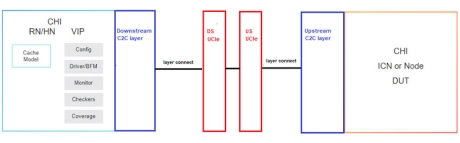

Simulation VIP for AMBA CHI-C2C

- Incorporating the latest protocol updates, the Cadence Verification IP for CHI-C2C provides a complete bus functional model (BFM), integrated automatic protocol checks, and a coverage model.

- Designed for easy integration in testbenches at IP, systems with multiple CPUs, accelerators, or other device chiplets, the VIP for CHI-C2C provides a highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms.

-

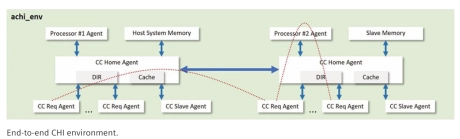

Verification IP for AMBA

- AMBA® ACE and CHI coherent interconnect technologies enable an entirely new class of high-performance datacenter applications in areas of machine learning, network processing, storage off-load, in-memory database, and 4G/5G wireless technology.

- Processor architectures and accelerators can now seamlessly operate over cache coherent intercon nects using the right combination of general-purpose processors and heterogeneous acceleration devices, such as FPGAs, GPUs, network/ storage adapters, intelligent networks, and custom ASICs.

-

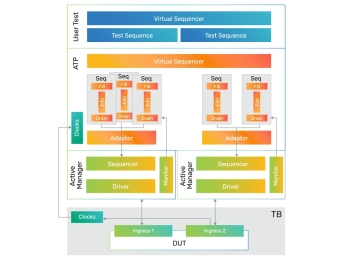

Simulation VIP for AMBA ATP

- Definition of Adaptive Traffic Profiles

- Definition of write and read traffic profiles using the ATP specification terminology

- Timing Control

- Support of primary and secondary timing parameters

-

DDR Controller supporting DDR5 with a CHI interface and Advanced Feature Package

- Supports JEDEC standard DDR5 and DDR4 SDRAMs and DIMMs

- Multiport Arm® AMBA® interface (4 AXI™/3 AXI™) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys DDR5/4 PHY or other DDR5/4 PHYs

- Best in class performance with unique features such as QoS-based scheduling and phase-aware scheduling