AI Connectivity IP

Filter

Compare

63

IP

from

10

vendors

(1

-

10)

-

224G SerDes PHY and controller for UALink for AI systems

- UALink, the standard for AI accelerator interconnects, facilitates this scalability by providing low-latency, high-bandwidth communication.

- As a member of the UALink Consortium, Cadence offers verified UALink IP subsystems, including controllers and silicon-proven PHYs, optimized for robust performance in both short and long-reach applications and delivering industry-leading power, performance, and area (PPA).

-

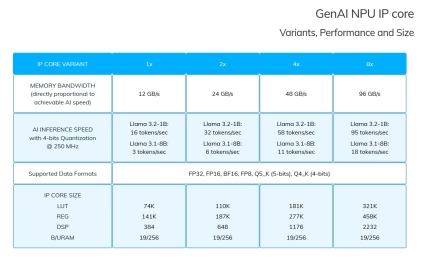

Embedded AI accelerator IP

- The GenAI IP is the smallest version of our NPU, tailored to small devices such as FPGAs and Adaptive SoCs, where the maximum Frequency is limited (<=250 MHz) and Memory Bandwidth is lower (<=100 GB/s).

-

ARC NPX Neural Processing Unit (NPU) IP supports the latest, most complex neural network models and addresses demands for real-time compute with ultra-low power consumption for AI applications

- ARC processor cores are optimized to deliver the best performance/power/area (PPA) efficiency in the industry for embedded SoCs. Designed from the start for power-sensitive embedded applications, ARC processors implement a Harvard architecture for higher performance through simultaneous instruction and data memory access, and a high-speed scalar pipeline for maximum power efficiency. The 32-bit RISC engine offers a mixed 16-bit/32-bit instruction set for greater code density in embedded systems.

- ARC's high degree of configurability and instruction set architecture (ISA) extensibility contribute to its best-in-class PPA efficiency. Designers have the ability to add or omit hardware features to optimize the core's PPA for their target application - no wasted gates. ARC users also have the ability to add their own custom instructions and hardware accelerators to the core, as well as tightly couple memory and peripherals, enabling dramatic improvements in performance and power-efficiency at both the processor and system levels.

- Complete and proven commercial and open source tool chains, optimized for ARC processors, give SoC designers the development environment they need to efficiently develop ARC-based systems that meet all of their PPA targets.

-

D2D Controller addon for D2D SR112G PHY with CXS interface

- Low Latency controller for die-to-die connectivity

- Supports PAM-4 and NRZ PHY signaling mode in all data rates

- Reduces BER with optional FEC configurations

- Supports Arm® AMBA® CXS interface

-

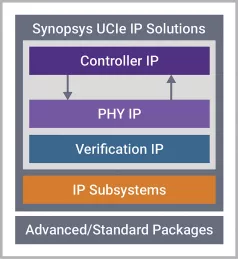

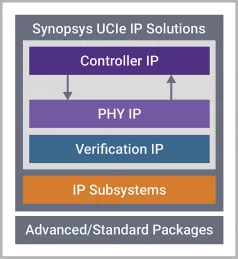

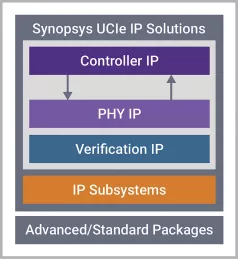

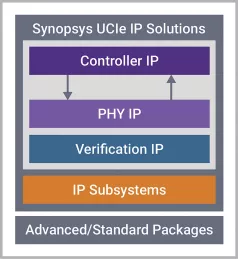

UCIe Chiplet PHY & Controller

- Compliant with the UCIe specification (2.0 & 1.1)

- Flexible Structure, easy to customize (Pre-hardened PHY tuned to Customer Spec, PHY + Adapter Layer, PHY + Adapter Layer + Customized Protocol Layer)

- Supports the CXS/AXI using the streaming package (AXI Interface bandwidth up to 89%)

-

Die-to-Die, High Bandwidth Interconnect PHY Ported to TSMC N7 X24

- Delivers up to 4Gbps per pin with up to bidirectional 2 Tbps/mm of die edge

- High-bandwidth, low-power, low-latency multi-channel PHY in applications requiring connections between dies within a package

- Compliant with Intel Advanced Interface Bus (AIB) v1.1 standard

- Compliant with IEEE 1149.1 (JTAG), 1149.6 (AC JTAG) for easy integration with SoC testability framework

-

Die-to-Die, High Bandwidth Interconnect PHY Ported to TSMC N5 X24, North/South (vertical) poly orientation

- Delivers up to 4Gbps per pin with up to bidirectional 2 Tbps/mm of die edge

- High-bandwidth, low-power, low-latency multi-channel PHY in applications requiring connections between dies within a package

- Compliant with Intel Advanced Interface Bus (AIB) v1.1 standard

- Compliant with IEEE 1149.1 (JTAG), 1149.6 (AC JTAG) for easy integration with SoC testability framework

-

Die-to-Die, AIB 2.0 PHY Ported to Intel 16, North/South (vertical) poly orientation

- Delivers up to 4Gbps per pin with up to bidirectional 2 Tbps/mm of die edge

- High-bandwidth, low-power, low-latency multi-channel PHY in applications requiring connections between dies within a package

- Compliant with Intel Advanced Interface Bus (AIB) v1.1 standard

- Compliant with IEEE 1149.1 (JTAG), 1149.6 (AC JTAG) for easy integration with SoC testability framework

-

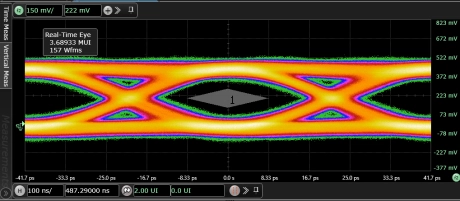

UCIe-S PHY for Standard Package (x32) in TSMC (N3P)

- Data rates up to 16Gbps per pin

- Self-contained hard macro

- Self-calibrating and training

- Side band channel for initialization and parameter exchange