7nm 58G DSP-based PAM4/NRZ SerDes IP

Filter

Compare

142

IP

from

26

vendors

(1

-

10)

-

1-56Gbps Serdes - 7nm (Multi-reference Clock)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (Ultra Low Latency)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (Area-optimized)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-112Gbps Serdes - 7nm

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (PPA-optimized)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

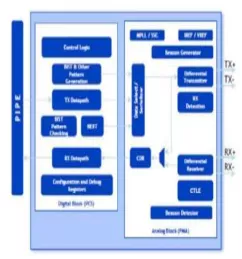

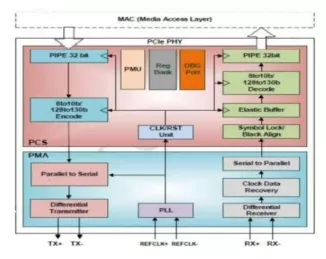

PCIe 2.0 Serdes PHY IP, Silicon Proven in TSMC 7nm

- Compatible with PCIe base Specification

- Full compatible with PIPE4.2 interface specification

- Independent channel power down control

- Implemented Receiver equalization Adaptive-CTLE to compensate insertion loss

-

SerDes PHY IP in TSMC (7nm, 12/16nm, 22nm, 28nm)

- Supports 1.25G to 10.3125Gbps data rates and compact die area

- Supports up to 25dB channel loss@ 5.15625GHz

- Supports RX loss-of-signal detection

- Supports X1, X2 and X4 lanes

-

PCIe 3.0 Serdes PHY IP, Silicon Proven in TSMC 7nm

- Compliant with PCIe 3.0 Base Specification

- Compliant with PIPE 4.3

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s and 8.0 GT/s

- Supported physical lane width: x4

-

PCIe 4.0 Serdes PHY IP Silicon Proven in TSMC 7nm

- Compliant with PCIe 4.0 Base Specification

- Compliant with PIPE 4.4

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s and 16.0 GT/s

- Supported physical lane width: x4

-

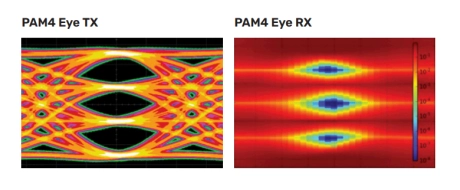

SerDes IP

- 10dB to 35dB bump-to-bump insertion loss

- Multi-rate support for 56Gbps to 112Gbps PAM4 and NRZ

- Integrated PLL

- Robust clock distribution architecture

- Advanced mixed signal analog equalization architecture

- Fully adaptive and programmable RX equalization

- Auto-negotiation

- Link Training