40nm ULP Memory IP

Filter

Compare

7

IP

from

5

vendors

(1

-

7)

-

FTP Non Volatile Memory for Standard TSMC 40nm ULP Process

- Ultra Low Power Read (30uA/MHz for 39b-IO) at 0.85V Single Power

- 10-Time Programmable

- > 10 years retention

-

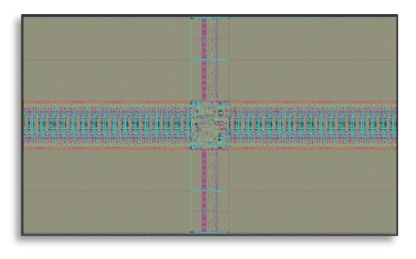

High Speed Single Port Compiler on TSMC 40nm ULP

- Low voltage

- Ultra low power data retention

- Self biasing

- Soft error immunity

-

4Kx32 Bits OTP (One-Time Programmable) IP, TSMC 40nm ULP 1.1V/2.5V Process

- Fully compatible with standard TSMC 40nm ULP 1.1V/2.5V CMOS logic process

- Low voltage: 1.1V+/-10% read and 2.65V+/-5% program

- High-speed program: 10us single-bit programming and up to 4-bit programming

- High-speed read: 25Mhz read clock (40ns cycle time) per 32-bit word

-

Memory Compilers

- Dolphin provides a wide range of Memory Compilers and Specialty Memory (ROM, Multi Port RF, CAM, etc.) optimized to meet even the most demanding requirements for high performance, high density and low power.

-

4608x12 Bits OTP (One-Time Programmable) IP, TSMC 40ULP 0.9V/2.5V Process

- Fully compatible with standard TSMC 40nm ULP 0.9V/2.5V CMOS logic process

- Low voltage: VDD 0.9 V ± 10% for read and program; VDDP: 1.71–3.60 V for read and 2.65 V ± 5% for program

- High speed program: 10-us programming time and support up to dual-bit concurrent programming at one CLK cycle

- High speed read: 10-MHz read clock (100-ns cycle time) per 12-bit word.

-

1Kx8 Bits OTP (One-Time Programmable) IP, TSMC 40ULP 1.1/2.5V Process

- Fully compatible with standard TSMC 40nm ULP 1.1V / 2.5V CMOS process

- Low voltage: VDD 1.1 V ± 10% read and VDDP 2.1 V ± 5% program

- High speed program: 10-us single-bit programming

- High speed read: 9-MHz read clock at 8-bit word.