10Gbps Ethernet IP

Filter

Compare

27

IP

from

13

vendors

(1

-

10)

-

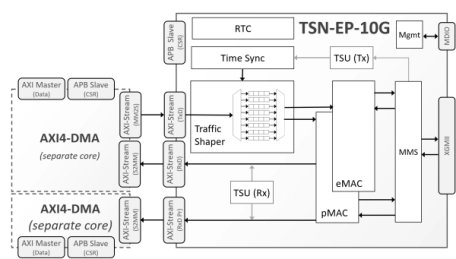

TSN Ethernet Endpoint Controller 10Gbps

- The TSN-EP-10G implements a configurable controller meant to ease the implementation of endpoints for networks complying with the Time Sensitive Networking (TSN) standards

- It integrates hardware stacks for timing synchronization (IEEE 802.1AS-2020) and traffic shaping (IEEE 802.1Qav and 802.1Qbv), frame-preemption (IEEE 802.1Qbu and IEEE 802.3br) and a low-latency Ethernet MAC.

-

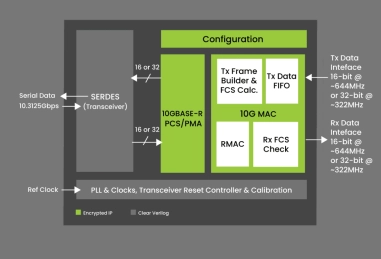

10-Gbps Ultra-Low Latency Ethernet MAC and PCS

- The core is designed using advanced design techniques leading to unmatched ultra-low gate count utilization and amazing latency performances.

- The 10G IP core support both 16b (644MHz) and 32b (322MHz) modes, and can support full wire line speed with a 64-byte packet length. It also supports back-to-back or mixed length traffic with no dropped packets.

-

10Gbps Low Latency Ethernet Solution

- Implements the full 802.3 specification with preamble/SFD generation, frame padding generation, CRC generation and checking on transmit and receive respectively.

- Implements 802.3bd specification with ability to generate and recognize PFC pause frames.

- Implements reconciliation sublayer functionality with start and terminate control characters alignment, error control character and fault sequence insertion and detection.

- Multiple user interface options for the MAC data path; AXI-4 streaming or Avalon Streaming; 32-bit data path 312.5MHz or 64-bit data path 156.25MHz

-

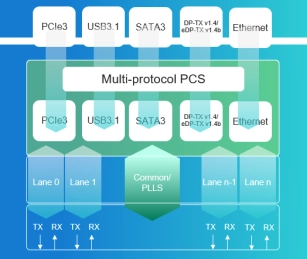

Ethernet SerDes - 16Gbps and 10Gbps multi-protocol SerDes PHY

- Wide range of protocols that support networking, HPC, and applications

- Low-latency, long-reach, and low-power modes

- Multi-Link PHY—mix protocols within the same macro

- EyeSurf —non-destructive on-chip oscilloscope

- Extensive set of isolation, test modes, and loop-backs including APB and JTAG

- Supports 16-bit, 20-bit, and 32-bit PIPE and non-PIPE interfaces

- Selectable serial pin polarity reversal for both transmit and receive paths

-

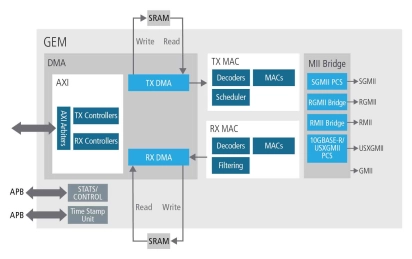

Ethernet Controller - Configurable MAC solutions for speeds from 10Gbps to 10Mbps

- High-performance DMA with advanced AXI offloading capabilities and descriptor caching, QoS, and IEEE1588

- Time-Sensitive Networking/Audio-Video Bridging (TSN/AVB) functionality enables unified Ethernet communication of critical data without traffic congestion in shared networks

- IEEE 802.3az Energy-Efficient Ethernet (EEE), VLAN, TCP/IP offload, and remote network monitoring (RMON)

- Multiple client interfaces: AXI, AHB, with optional DMA support

-

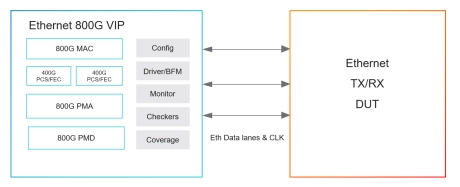

Simulation VIP for Ethernet up to 800G

- 800Gbps Interfaces

- 800Gbps Ethernet interfaces based on Ethernet Technology Consortium supports:

- 800GMII

- 800GBase-R Dual-PCS 32 lanes (25Gb/s)

-

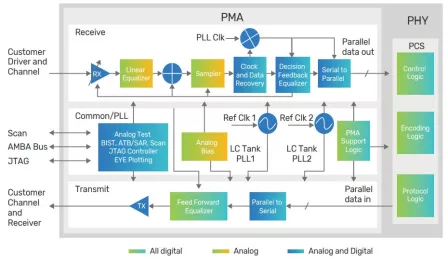

10Gbps Multi-Protocol PHY IP (+PCIe 3.1)

- Supports 10G-KR, PCIe 3.1/2.0/1.0, XAUI, Q/SGMII, and Gigabit Ethernet

- LC tank PLL with a wide range of reference clock frequencies and SSC

- High-performance decision feedback equalization and adaptive CTLE

- Serial and parallel loop-back functions

- Available in X1 through X10 lane configurations

-

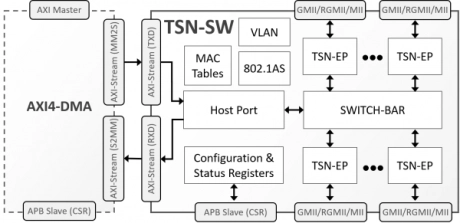

Multiport TSN Ethernet Switch

- The TSN-SW implements a highly flexible, low-latency, multiport TSN Ethernet switch.

- It supports the hardware functionality for Ethernet bridging according to the IEEE 802.1Q standard and implements the essential TSN timing synchronization and traffic-shaping protocols (i.e. IEEE 802.1AS-2020, 802.1Qav, 802.1Qbv, and 802.1Qbu, 802.1br).

-

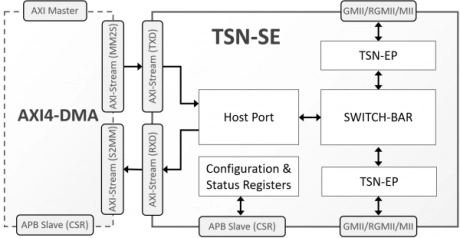

TSN Ethernet Switched Endpoint Controller

- The TSN-SE implements a configurable controller meant to ease the implementation of switched endpoints for Time Sensitive Net-working (TSN) Ethernet networks.

- It integrates hardware stacks for timing synchronization (IEEE 802.1AS-2020), traffic shaping (IEEE 802.1Qav and IEEE 802.1Qbv), frame-preemption (IEEE 802.1Qbu and IEEE 802.3br) and a low-latency Ethernet MAC.

-

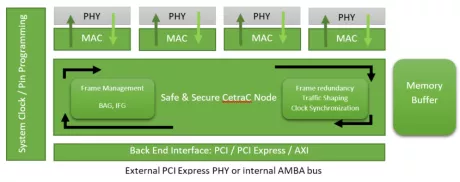

Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network

- "Ethernet/TSN/ARINC664P7 EndSystem with customizable number of ports up to 1 Gbps.

- Support IEEE 1588 PTPV2 as GrandMaster or User

- Safe & Secure Ethernet communication

- Multi-protocol