10 100 1000M Ethernet PHY IP

Filter

Compare

11

IP

from

7

vendors

(1

-

10)

-

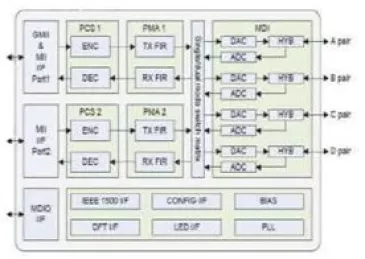

GbE (10/100/1000 Base-T) PHY IP, Silicon Proven in SAM 14LPP

- EEE 802.3-2008, IEEE 802.3az fully standards compliant

- IEEE 1588-2008 support

- BroadR-Reach™ support

- Dual port MAC interface:

-

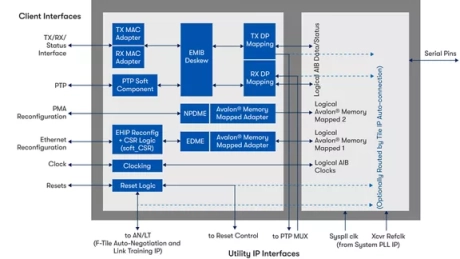

Intel® Agilex™ 7 F-Tile Ethernet Hard IP

- The Intel® Agilex™ 7 FPGA F-Tile incorporates a fracturable, configurable, hardened Ethernet protocol stack for supporting rates from 10G to 400G, compatible with IEEE 802.3 specification, and other related Ethernet Consortium specifications.

-

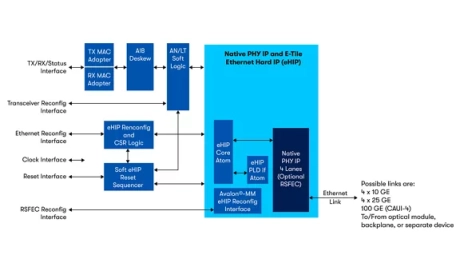

Intel® Agilex™ 7 and Intel® Stratix® 10 FPGA E-Tile Hard IP

- The Intel® Agilex™ 7 and Intel® Stratix® 10 FPGA E-Tile incorporates a configurable, hardened Ethernet protocol stack compatible with the IEEE 802.3 High-Speed Ethernet Standard and the 25G and 50G Ethernet Specification, Draft 1.6 from the 25G Ethernet Consortium

- The Intellectual Property (IP) core provides access to this hard IP at data rates of 10 Gbps, 25 Gbps, and 100 Gbps.

-

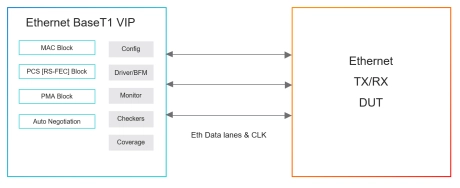

Simulation VIP for Ethernet Base-T1

- 10 Base-T1s Interface

- Based on IEEE 802.3cg-2019 (Clause 147)

- 4b/5b Encoder/Decoder

- 17bit self-synchronizing scrambler/descrambler

-

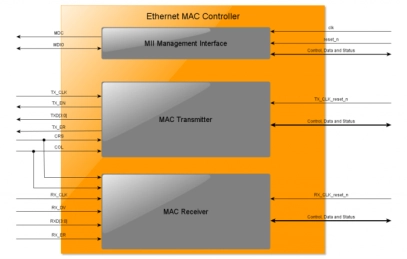

10/100/1000 Ethernet MAC DO-254 IP Core

- The 10/100/1000 Ethernet MAC Controller DO-254 IP Core implements the Media Access Control as specified in the IEEE 802.3-2008 specification.

- The Ethernet MAC Controller has been developed to DAL A according to the DO-254 / ED-80 and is accompanied by a Certification Kit.

-

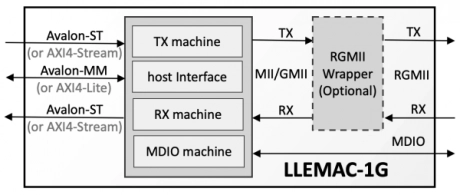

Low-Latency 10/100/1000 Ethernet MAC

- The LLEMAC-1G implements an Ethernet Media Access Controller (MAC) compatible with the 10/100 Mbps IEEE 802.3 and 1Gbps IEEE 802.3-2002 specifications.

- Featuring extremely low egress and ingress latency, the core is ideal for the implementation of TSN Ethernet nodes, live streaming and other devices requiring minimum latency in the reception and transition of Ethernet frames.

-

MAC 10/100/1000 Ethernet Controller

- IEEE 802.3-2002 specification with preamble, start-of-frame delimiter (SFD), frame padding generation and cyclic redundancy code (CRC) generation and checking is fully implemented

- Supports 10/100 Mbps or 1000 Mbps operation (selectable via a core configuration registers)

- Supports full- and half-duplex operation (selectable via a core configuration registers)

- CSMA/CD protocol for half-duplex operation

-

Tri-Mode Ethernet Media Access Controller (TEMAC)

- Designed to IEEE 802.3-2012 specification

- Supports 10/100/1000/2500 Mbps Ethernet

- Configurable half-duplex and full-duplex operation

- Configured and monitored through an optional independent microprocessor-neutral interface

-

Ethernet 1G/2.5G BASE-X PCS/PMA or SGMII

- Designed to IEEE 802.3-2012 specification

- Full-duplex operation

- Supports speeds up to 2.5 Gigabit per second

- Supports Select I/O or Transceiver implementations

-

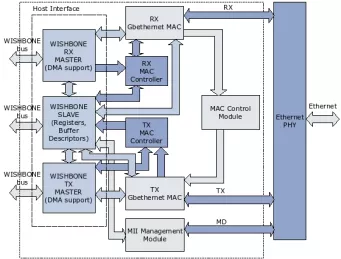

XPS_LL_TEMAC

- Independent 2K, 4K, 8K, 16K, or 32K Byte TX and RX data FIFOs for queueing frames

- Filtering of "bad" receive frames

- Support for several PHY interfaces

- Media Independent Interface Management access to PHY registers