MIPI SoundWire IP

MIPI SoundWire IP is a high-performance interface designed to enable efficient, low-latency audio communication between processors and audio peripherals in mobile and embedded devices. As part of the MIPI (Mobile Industry Processor Interface) standard, MIPI SoundWire IP supports high-quality, multi-channel audio transmission, making it ideal for applications such as smartphones, wearables, automotive infotainment systems, and smart home devices.

All offers in

MIPI SoundWire IP

Filter

Compare

17

MIPI SoundWire IP

from

5

vendors

(1

-

10)

-

MIPI SoundWire I3S Manager IP

- The MIPI SoundWire I3S Manager IP enables efficient, low-power, and high-fidelity audio data transfer for mobile, consumer, and automotive applications.

- Compliant with the MIPI SoundWire I3S (Inter-IC Sound) standards, it supports synchronized, multi-channel audio over a scalable two-wire interface, ideal for connecting digital microphones, amplifiers, and codecs in space-constrained designs.

-

MIPI SoundWire I3S Peripheral IP

- The MIPI SoundWire I3S Peripheral IP delivers seamless, low-power, and high-quality audio connectivity for a range of mobile, consumer, and automotive devices.

- Fully compliant with the MIPI SoundWire I3S (Inter-IC Sound) specifications, it enables synchronized, multi-channel audio communication with a compact and efficient two-wire interface, ideal for integrating digital microphones, amplifiers, or audio codecs.

-

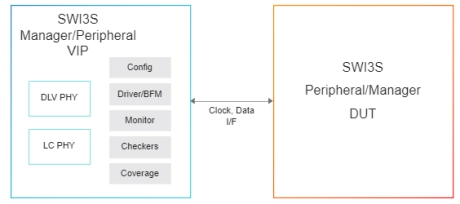

MIPI SoundWire I3S Verification IP

- Full MIPI SoundWire I3S Master, Slave and Monitor functionality

- Supports MIPI Soundwire-I3S Bus Draft Specification v0.4r06.

- Supports system with one master and one or more slaves (upto 8 slaves).

- Supports LVDS PHY for higher speed and a single-ended CMOS PHY for lower speed systems.

-

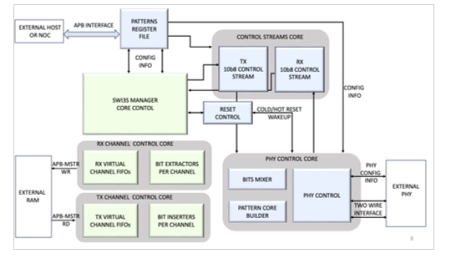

MIPI SWI3S Manager Core IP

- The SWI3S (SoundWire I3S Interface) Manager Controller Core IP implements the link protocol to communicate in half-duplex fashion to transfer the Audio streams and the Control information together.

- One or more SWI3S Peripheral IP can be connected specific to the application.

-

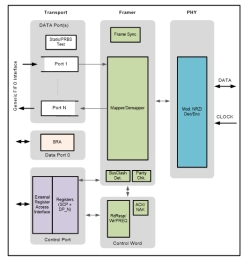

MIPI SoundWire Slave Controller 1.2

- MIPI SoundWire®Slave Controller, typically integrated into audio DSP/Codecs or directly into audio peripherals such as Microphones and Amplifiers used in smart phones, tablets and mobile PCs.

- The IP when integrated provides SoundWire, a new audio interface to connect to Master typically embedded in Application Processor or Audio Codecs.

-

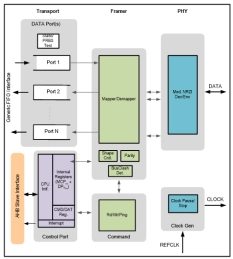

MIPI SoundWire Master Controller 1.2

- Compliant with MIPI SoundWire specification version 1.2

- Configurable number of Data Ports Configurable Direction – Source or Sink

- Implements clock gearbox with programmable frequency divider

- Implements SoundWire Bus Clock Stop and WakeUp detection

-

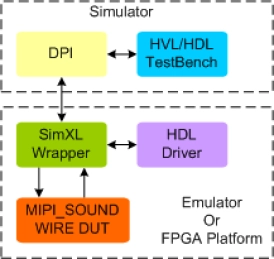

Simulation VIP for MIPI SoundWire-I3S

- PHYs

- Supports LC PHY and DLV PHY

- Interfaces

- Supports serial interface

-

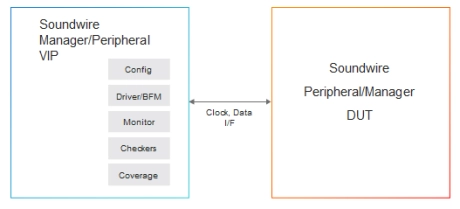

Simulation VIP for MIPI SoundWire

- Multi-lane Payload Transport

- Up to 8 data lanes are supported

- High-PHY Mode

- High-performance PHY

-

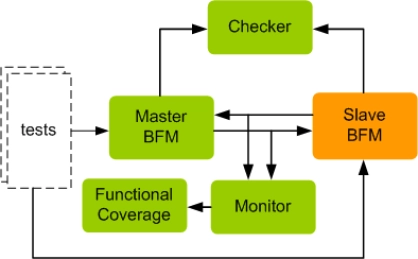

MIPI SoundWire Verification IP

- Full MIPI SoundWire Master, slave and Monitor functionality

- Supports MIPI SoundWire version 1.2r08 Specifications

- Supports Basic PHY and High PHY mode

- Supports IO timing

-

MIPI SOUNDWIRE Synthesizable Transactor

- Supports MIPI SoundWire version 1.2r08 Specifications

- Supports full MIPI SoundWire Master,Slave functionality

- Supports Basic PHY and High PHY mode

- Supports IO timing