JESD204 IP

The JESD204 IP cores are high-speed point-to-point serial interfaces for digital-to-analog (DAC) or analog-to-digital (ADC) converters to transfer data to FPGA devices.

Explore our vast directory of JESD204 IP cores below.

All offers in

JESD204 IP

Filter

Compare

40

JESD204 IP

from

13

vendors

(1

-

10)

-

JESD204E Controller IP

- The JESD204E Controller IP from Chip Interfaces is an early adopter’s version of the upcoming revision of the JEDEC standard for Serial Interface for Data Converters.

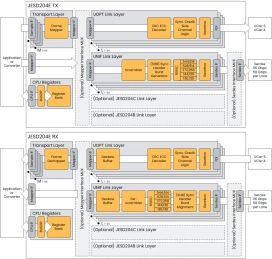

- The JESD204-E IP core supports the UCIe Optimized Link Layer, a dedicated mode to run JESD over UCIe Modules with Line rates up the 64Gbps per bump, and a JESD204D backwards compatible mode called the Unified Link Layer with line speeds up to 116Gbps with PAM4 and 58Gbps with NRZ and full FEC support.

-

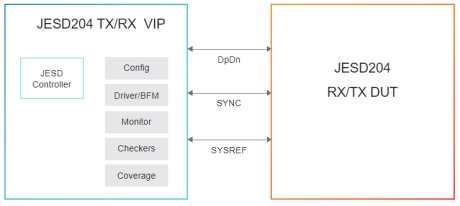

JESD204D Verification IP

- Truechip JESD204D VIP is compliant to the latest JESD204D,C.01,C &B specification by JEDEC

- It is also backward compatible with all the previous versions of JESD204

- Supports a wide range configurations for data converter devices

- Over single and multiple serial links with each link can support single or multiple lanes as per requirements

-

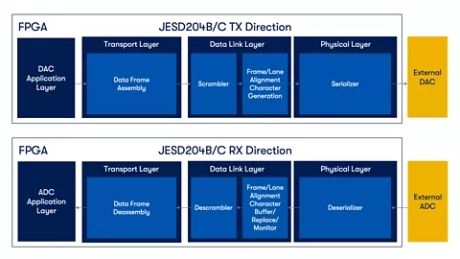

JESD204 FPGA IP

- The JEDEC committee created the JESD204 data converter serial interface standard to standardize and reduce the number of data inputs/outputs between high-speed data converters and other devices, such as FPGAs

- The protocol has many advantages, such as simplified layouts, skew management, and deterministic latency.

-

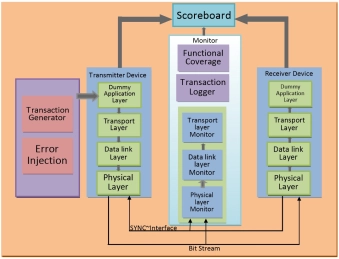

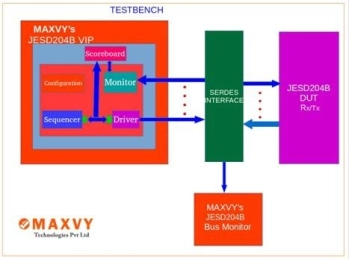

JESD204B UVM VIP

- The vendor provides configurable JESD204B TX/RX verification IP

- JESD204B is a Serial Interface for Data Converters which are defined by JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

- Our VIP covers Transport and Data link layer functionality of JESD204B

- The VIP provides more flexible configuration to user to select their needs like lane,device configuration, data width

-

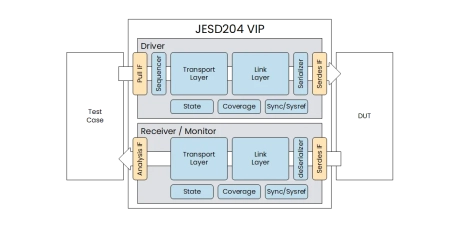

JESD204 Verification IP

- This JESD204 Verification IP provides an advanced and efficient solution for verifying and debugging these standards in a UVM simulation environment.

- The verification IP helps reduce time to test, accelerate verification process and ensures a high quality for the end-product.

-

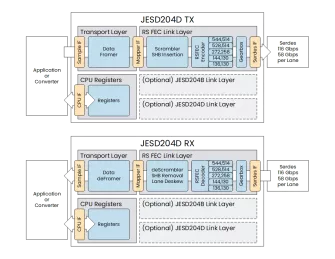

JESD204D Controller IP

- Line rates up to 116 Gbps

- Supports 1-24 lanes

- Supports 1-96 converters

- HD-mode supported

-

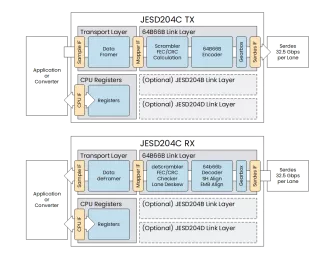

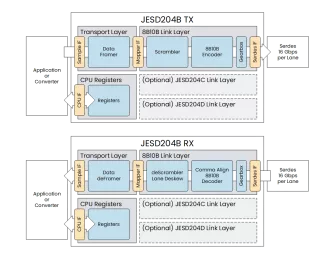

JESD204C Controller IP

- Designed to JEDEC JESD204C.1 specification

- Line rates from 1 Gbps to 32.5 Gbps

- Supports 1-24 lanes

- Supports 1-96 converters

-

JESD204B Controller IP

- Designed to JEDEC JESD204B.01 specification

- Line rates from 1 Gbps to 12.5 Gbps (with optional extension to 16 Gbps)

- Supports 1-24 lanes

- Supports 1-96 converters

-

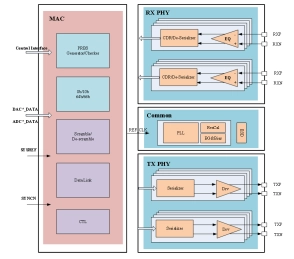

JESD204B/204C IP with PHY and MAC layer

- X4/X8 Lane Mode, support up to 25Gbps (per lane)

- Shared common PLL based architecture

- Digitally-control-impedance termination resistors and On-chip resistance calibration

- Configurable TX output differential voltage swing

-

Simulation VIP for JESD204

- Topology

- Transmitter or receiver configuration

- Clock Frequency

- Any frequency is supported, as the VIP works on the source clock