ADC / DAC IP for Tower

Welcome to the ultimate

ADC / DAC IP

for

Tower

hub! Explore our vast directory of

ADC / DAC IP

for

Tower

All offers in

ADC / DAC IP

for

Tower

Filter

Compare

7

ADC / DAC IP

for

Tower

from

5

vendors

(1

-

7)

-

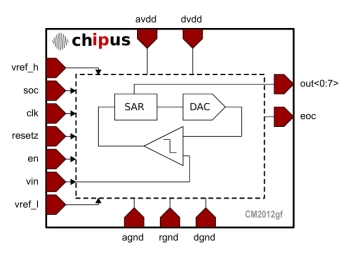

Low-Power 8-bit SAR ADC - 8 bits, 50kSPS, Low Voltage (1.8V), Low Power (20µA) TowerJazz 0.18 um

- This macro-cell is a low power, general purpose, 8-bit, 50kSPS, Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) core designed for TowerJazz 0.18μm TS18SL CMOS technology.

- The circuit has an internal sample-and-hold circuit and a power-down operation mode to save power in applications where power consumption is critical.

-

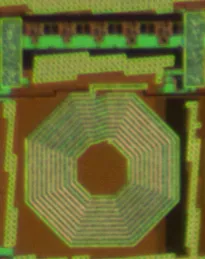

Super Inductor IP

- High Inductor Q (10 to 50)

- High Inductor Bandwidth (2.5Ghz to 50Ghz)

- Stackable Design

-

14-bit 12.5MSPS SAR ADC - Tower 65nm

- The A14B12p5M is a high-performance, low-power analog-to-digital converter (ADC) intellectual property (IP) block designed for applications requiring both high speed and power efficiency.

- It offers 14-bit resolution with maximum sampling rate of 12.5 megasamples per second (MS/s), making it ideal for RF communications, radar sensing, and aerospace and defense applications.

-

10-bit Pipeline ADC - Tower 180 nm

- 10-bit resolution

- 25 MSPS sampling rate

- 6 mW power

- 25 MHz Input Bandwidth

-

10-Bit Current steering DAC - TowerJazz 0.18um

- Area: 0.088mm2

- Fsmax (Maximum sampling frequency): 16MS/s

- Idd (Current consumption): 3mA

- Resolution (Input digital data resolution): 10bits

-

13 bits 2.56MS/s SAR ADC - TowerJazz 0.18um

- Area: 0.178mm2

- Fsmax (Maximum sampling frequency): 2.56MS/s

- Idd (Current consumption): 2mA

- Resolution (Output digital data resolution): 13bits