Serdes IP for SMIC

Welcome to the ultimate

Serdes IP

for

SMIC

hub! Explore our vast directory of

Serdes IP

for

SMIC

All offers in

Serdes IP

for

SMIC

Filter

Compare

15

Serdes IP

for

SMIC

from

5

vendors

(1

-

10)

-

4.25 Gbps Multi-Standard SerDes

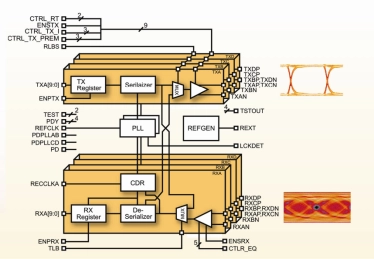

- The MXL4254A is a silicon proven Quad Gigabit SerDes implemented in digital CMOS technology. Each of the four channels supports data rate up to 4.25 Gbps.It is compatible with router-backplane links, PCI Express, SATA, RapidIO, 10 Gbps Ethernet (XAUI), FibreChannel, SFI-5, SPI-5, and other communication applications.

-

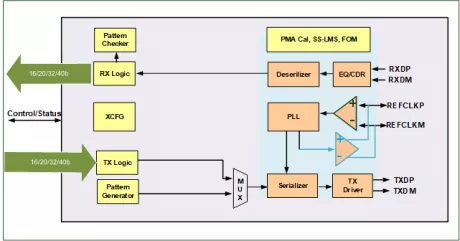

10G Combo Serdes for USB/PCIe/Ethernet, SMIC 14FF, N/S orientation

- Supports 1.25G to 10.3125Gbps data rates and compact die area

- Supports up to 25dB channel loss@ 5.15625GHz

- Supports RX loss-of-signal detection

- Supports X1, X2 and X4 lanes

-

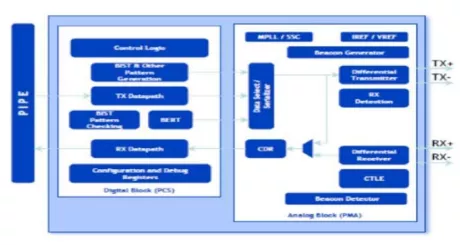

PCIe 2.0 Serdes PHY IP, Silicon Proven in SMIC 28HKMG

- Compatible with PCIe base Specification

- Full compatible with PIPE4.2 interface specification

- Independent channel power down control

- Implemented Receiver equalization Adaptive-CTLE to compensate insertion loss

-

PCIe 3.0 Serdes PHY IP, Silicon Proven in SMIC 28SF

- Silicon Proven in SMIC 28SF with 0.8V and 1.8V power supply.

- Compatible with PCIe base Specification

- Support 32-bit/16-bit parallel interface

- Support for PCIe3(8.0Gbps)

-

12G Multiprotocol Serdes IP, Silicon Proven in SMIC 14SF+

- A universal SERDES IP that operation from 1Gbps to 12.5 Gbps

- Compatible with PCIe/USB3/SATA base Specification

- Support 40-bit/32-bit/20-bit/16-bit parallel interface

- Support for PCIe2(5.0Gbps), USB3.0(5.0Gbps) and SATA3(6.0Gbps)

-

8G Multiprotocol Serdes IP, Silicon Proven in SMIC 14SF+

- Area: ~0.3mm2 per-lane

- Silicon Proven in SMIC14SF+/SF++ with 0.8V and 1.8V power supply

- Support for SATA3(6.0Gbps) and PCIe3(8.0Gbps)?

- Backward compatible with 1.5Gbps, 3.0bps for SATA

-

Serdes - SMIC 55nm Eflash

- 4 TX channels and 4 RX channels;Supports 1.25G~6.25Gbps operation

- Internal high performance low jitter PLL:RMS jitter < 1.5ps @6.25GHz

-

FPD-link, 30-Bit Color LVDS Receiver, 40-170Mhz (Full-HDTV @60Hz) LVDS SerDes 5:35 channel decompression with deskew capability

- 1P7M/1P8M/1P9M/1P10M layout structure based on 65nm Logic 1P10M Salicide 1.2V/2.5V process.

- 1.2V/2.5V ±10% supply voltage, -40/+125°C

- Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard 1596.3- 1996+ ANSI/TIA/EIA-644-A Specifications.

- Up to 5.6Gbps bandwidth (40 to 170Mhz pixel clock) ( supports Full HDTV 1080p )

-

Dual FPD-link, 30-Bit Color LVDS Receiver, 40-170Mhz (Full-HDTV @120Hz) LVDS SerDes 10:70 channel decompression with deskew capability

- 1P7M/1P8M/1P9M/1P10M layout structure based on 65nm Logic 1P10M Salicide 1.2V/2.5V process

- 1.2V/2.5V ±10% supply voltage, -40/+125°C

- Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard 1596.3- 1996+ ANSI/TIA/EIA-644-A Specifications.

- Up to 11.9Gbps bandwidth (40 to 170Mhz pixel clock) per pixel channel (Full HD @ 120Hz)

-

Dual FPD-link, 30-Bit Color LVDS Transmitter, 40-170Mhz (Full-HD @120Hz) - with 2 independant links capability LVDS SerDes 70:10 channel compression

- 1P7M/1P8M/1P9M/1P10M layout structure based on 65nm Logic 1P10M Salicide 1.2V/2.5V process.

- 1.2V/2.5V ±10% supply voltage, -40/+125°C

- Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard 1596.3-1996+ ANSI/TIA/EIA-644-A Specifications.

- Up to 11.9Gbps bandwidth (40 to 170Mhz pixel clock) per pixel channel (Full HD @ 120Hz)