Power Management IP for SMIC

Welcome to the ultimate

Power Management IP

for

SMIC

hub! Explore our vast directory of

Power Management IP

for

SMIC

All offers in

Power Management IP

for

SMIC

Filter

Compare

127

Power Management IP

for

SMIC

from

12

vendors

(1

-

10)

-

-

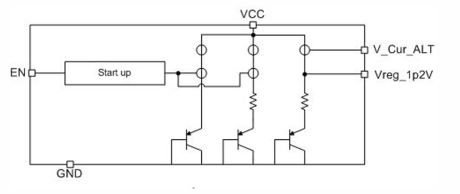

75mA Core Voltage Regulator

- Input voltage range 3.0V – 3.3V.

- Output voltage 1.2V or 1.8V ±4%.

- Output short circuit protection.

- Bundled with Obsidian 1.2V bandgap reference.

- Power down/enable input.

- Fast response to current steps.

-

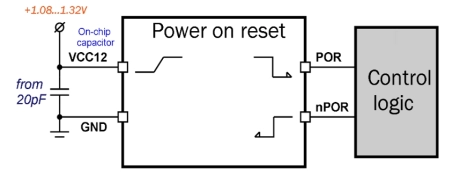

Power On Reset

- Input threshold 2VT.

- Reset and reset bar output logic levels.

- Minimum 8uS reset pulse for any power rise time.

- 1µA typical supply current.

- -40°C to 120°C temperature operation.

-

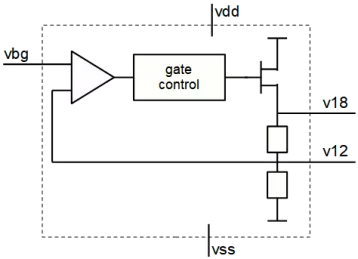

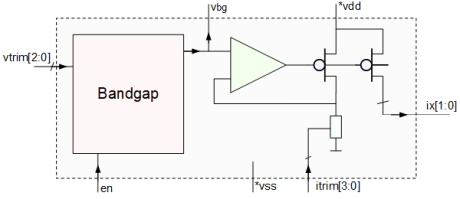

TSMC 180nm 5V Bandgap

- 2.5V-5.5V operation.

- 3σ 4% untrimmed voltage reference accuracy.

- 2% variation over -40ºC to 125ºC after trimming.

- 70dB low frequency PSRR.

- Trimmed, temperature compensated, 10µA reference current outputs with 3% accuracy.

- Trimmed IPTAT output currents can be provided.

- Less than 8µV noise from 0.1Hz to 10KHz.

-

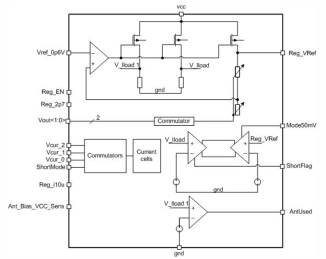

LDO voltage regulator (output voltage value 1.8 V, 2.4 V, 2.7 V, 3.0 V)

- SMIC CMOS 0.18 um

- High precision stabilization voltage

- Several operating modes

- Differential output voltage value (1.8 V, 2.4 V, 2.7 V, 3.0 V)

-

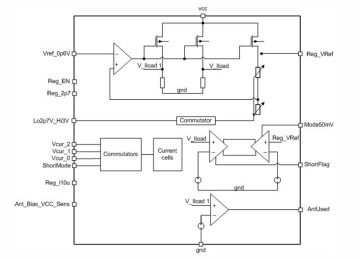

LDO voltage regulator (output voltage value 2.7 V, 3.0 V)

- SMIC CMOS 0.18 um technology

- High precision stabilization voltage

- Several operating modes

- Different output voltage value (2.7 V, 3.0 V)

-

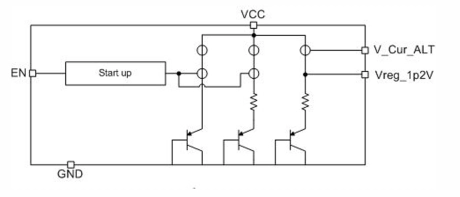

1.2 V Bandgap voltage reference

- SMIC CMOS 0.18µm

- Output voltage 1.2 V

- Temperature-compensated voltage in a wide temperature range

- Usage of bipolar pnp transistors

-

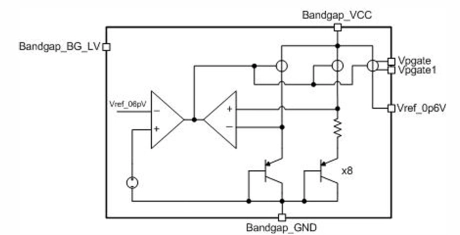

0.6 V Bandgap voltage reference

- SMIC CMOS 0.18µm

- Output voltage 0.6 V

- Temperature-compensated voltage in a wide temperature range

- Low supply voltage systems availability

-

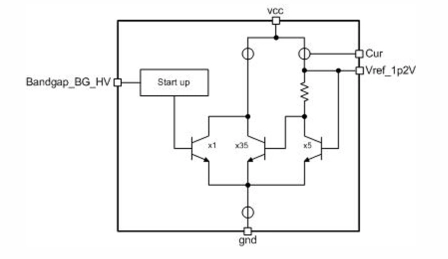

1.2 V Bandgap voltage reference

- SMIC CMOS 0.18 um

- Output voltage 1.2 V

- Temperature-compensated voltage in a wide temperature range

- Low current consumption

-

1.22 V Reference voltage source

- SMIC CMOS 0.18 um

- Output voltage 1.2 V

- Temperature-compensated voltage in a wide temperature range

- Usage of bipolar pnp transistors