Power Management IP for Samsung

Welcome to the ultimate

Power Management IP

for

Samsung

hub! Explore our vast directory of

Power Management IP

for

Samsung

All offers in

Power Management IP

for

Samsung

Filter

Compare

15

Power Management IP

for

Samsung

from

6

vendors

(1

-

10)

-

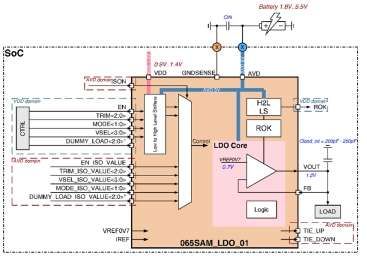

50 mA LDO voltage regulator (output voltage 0.9V/1.2V/1.34V) on Samsung 65nm

- 065SAM_LDO_01 is a low drop out voltage regulator designed to supply integrated circuits with stable and precise voltage.

- The LDO inputs voltage AVD from 1.8V to 5.5V and converts this voltage into a voltage VOUT 0.9V/1.2V/1.35V with 50mA load capacity.

- A Regulation OK (ROK) signal inform the system that LDO has completed its booting sequence and if its output is maintaining regulation for the current drawn by the load.

-

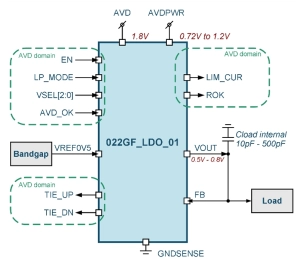

50mA capacitor-less LDO voltage regulator (output voltage 0.5V to 0.8V)

- GF 22nm FDX

- 0.72V – 1.2V input voltage range

- Programmable output voltage from 0.5 to 0.8V

- Normal and LP modes

-

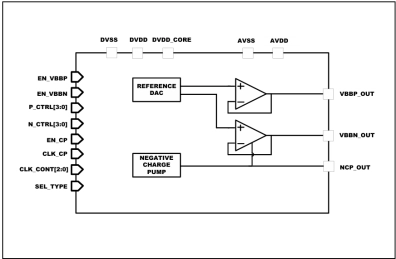

Adaptive Body Bias Generator on Samsung 28nm LN28FDS

- The adaptive body bias generator (ABBG) consists of a positive-BBG and a negative-BBG for FDSOI-MOS transistors.

- The ABBG is used for either Reverse Body Biasing (RBB) to reduce leakage current of the logic devices or Forward Body Biasing (FBB) to improve the system performance by adjusting the body voltages of transistors.

-

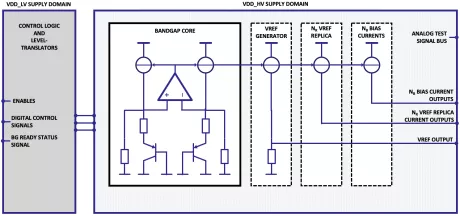

Low Power BandGap

- The agileREF_LP consists of: A bandgap reference core; A bandgap reference voltage generator (VREF) (Reference current outputs allow for remote reconstruction of an accurate reference voltage.) Bias current generators (IBIAS) (Temperature independent bias current generators)

-

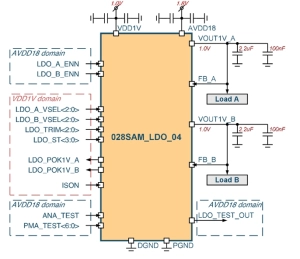

30mA 2-channel LDO voltage regulator (output voltage each channel 1.0V)

- Samsung 28nm FD-SOI

- 1.8V analog input voltage

- 1.0V digital input voltage

-

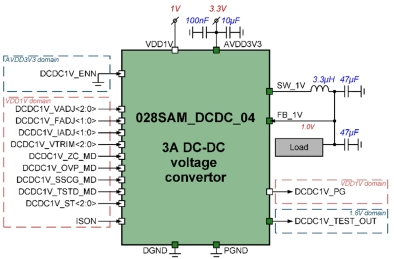

3.3V to 1.0V, 3.0A Step-down DC-DC converter

- Supply voltage: 3.3V analog and 1.0V digital

- Adjustable output voltage with trimming: 0.8V÷1.15V (1.0V typical)

- Maximum output current up to 3A

-

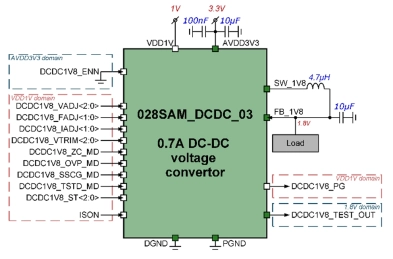

3.3V to 1.8V, 0.7A Step-down DC-DC converter

- Supply voltage: 3.3V analog and 1.0V digital

- Adjustable output voltage with trimming: 1.75V÷2.05V (1.8V typical)

- Output current 0.7A

- Soft start mode

-

Scalable, On-Die Voltage Regulation

- Droop and DFS/DVFS response profile

- Programmable droop and DFS/DVFS response rate

-

Low-power Power-On-reset design in Samsung Foundries 65nm LFR6LP process

- Low-power power-on-reset solution for power-critical IoT applications (50 nA operating current)