USB 2.0 Function Controller Checker OVA IP is fully documented, off the shelf component for the Developers of the USB 2.0 compliant Function Controller.

USB 2.0 OpenVera Assertions based Checker IP provides a concise, declarative mechanism to code the specification of sequences of events and activities of USB 2.0 Bus Protocol.

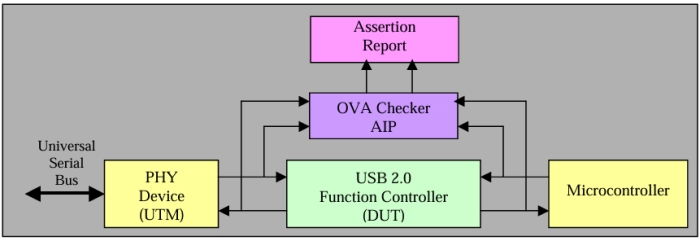

USB 2.0 OVA protocol rule Checker can work in a standalone mode i.e., can be plugged in any design verification environment, which uses the standard Protocol without disturbing the structure.

USB 2.0 OVA AIP Checker is developed using the abstraction in OVA syntax that is used in dynamic simulation of USB 2.0 based design.

OpenVera Assertions (OVA) provide fast and accurate way to simplify and speed up the device verification task. In a complex design process, verification may take up to 70% of the development time. OVA Checker AIP speeds up the verification process, thereby optimizing cost and time to market.

Product Specifications

- The AIP can be adapted to test a standard USB device in Synopsys Magellan Formal Verification environment.

- Supports PING Protocol.

- Supports SPLIT transactions.

- Supports SPLIT transactions.

Layered Approach

- A layered approach has been implemented in USB 2.0 OVA model to create a verification environment that allows sophisticated test scenarios.

- Layer 0: Logic and Events definitions - Booleans, events and variable definitions that are common to all USB 2.0 compliant devices are specified here.

- Layer 1: Individual templates for each of the Property corresponding to USB device are located in this layer.

- Layer 2: The common template from Layer 0 and individual templates from Layer 1 are instantiated here.

- Layer 3: This layer contains the `bind´ constructs meant for the OVA AIP Units and customized OVA AIP Header declarations.