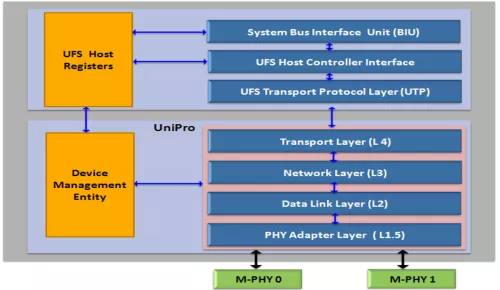

The UFS Host -UniPro IP is a simple, high performance, serial interface used primarily in mobile systems between host processing and NVM mass storage devices. The UFS uses UniPro as the datalink layer.

UFS 3.1 Host Controller compatible with M-PHY 4.1 and UniPro 1.8

Overview

Key Features

- Interface

- Master Interface - AXI [Optional - AHB, OCP].

- Slave Interface - AHB [Optional - AXI, OCP]

- UFS Host Features

- Support UFS Command Set layer, Device and Task manager

- Support for multiple commands and tasks.

- Optional support for Encryption engine.

- Unipro lane and power mode

- Multi-lane support [Optional - 1, 2, 3 or 4 lanes].

- Low power with multiple power operating modes.

- Logical lane mapping is not supported

- Unipro traffic class

- Support TC0 traffic class.

- Pre-emption.

- MIPI MPHY

- MPHY Type I support.

- Miscellaneous

- Configurable Transmit and Receive FIFOs.

- Detection of various errors and autonomous reaction to them is supported.

- AXI Master Interface

- UFS Host Controller initiator interface will only request the bus when there is sufficient space or data available to complete the requested read or write operation (no idle cycle between WR data of the same transaction if the interconnect can accept it)

- Write Interleave depth = 1

- All burst transfers are performed with a start address which is always aligned to the size of the transfer. The unaligned address is down aligned to the DWORD or QWORD boundary (depending on the bus width), and then a request can be sent for a burst transfer. For a read, it is masked. For a write, WSTRB signal is used

- Maximum burst size supported for 32 bit - 16x32b, Maximum burst size supported for 64 bit - 16x64b, Maximum burst size supported for 128 bit - 16x128b

- Supports only AxBURST value b01, indicating INCREMENTING transfers

- Supports only AxSIZE values b010, b011, and b100 indicating 4 bytes, 8 bytes and 16 bytes respectively, in a transfer

- The max value used in burst length is 'b1111 (i.e max value used in AxLEN is 'b1111)

- Burst length with less than max is used in AxLEN if transfer count reaches less than maximum for any descriptor fetch or UPIU transaction AHB Slave Interface

- AHB Slave supports only single transaction and do not support Burst.

- HRESP is 2-bits, but only OKAY (00) and ERROR (01) is being used, as AHB is for Register access only"

- Supports only single transfers of SINGLE burst type

- Supports only HSIZE value of b010, indicating 4 bytes in the single transfer

Benefits

- Seamless integration from PHY to Software

- Assured compliance across all components

- Single point of support

- Easiest acquisition process (one licensing source)

- Lowest overall cost including cost of integration

- Lowest risk for fast time to market

Block Diagram

Deliverables

- Synthesizable RMM compliant Verilog RTL code.

- Easy-to-use comprehensive OVM/UVM based randomized test environment

- Synthesis scripts

- Technical documents

- User guide

Technical Specifications

Foundry, Node

TSMC & GF

Availability

Now

Related IPs

- UFS 2.1 Host Controller compatible with M-PHY 3.1 and UniPro 1.6

- UFS 2.1 Device Controller compatible with MIPI M-PHY 3.1 and UniPro 1.6

- MIPI UFS v2.1 Host Controller IP, Compatible with M-PHY and Unipro

- UFS 3.0 Host Controller compatible with M-PHY 4.0 and UniPro 1.8

- UFS 3.0 Host Controller with AES Encryption compatible with M-PHY 4.0 and UniPro 1.8

- MIPI UFS v3.1 Host Controller IP, Compatible with M-PHY and Unipro