Inicore’s iniSCI Slave is a synthesizable, flexible, and structured VHDL implementation of a Serial Controller Interface (SCI) that uses a two-wire bus for communicating between integrated circuits or standard peripherals like smart LCDs and keypads.

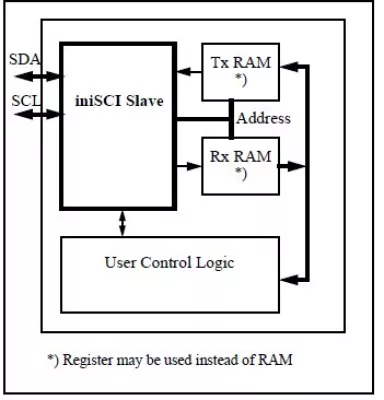

The iniSCI Slave complies with the definition of the ‘Inter-Integrated Circuit Bus’ (I2C). It is intended to be used as an interface block between the I2C buslines (SDA,SCL) and two mailbox memories. A local Mail-bus interface consisting of data, address and control lines allows you to interface registers or RAM’s up to a size of 256 bytes.

The iniSCI Slave contains the entire physical and data link layers, allowing to handle bus timing and frame generation/extraction, and thus reducing overhead from the system application.

INICORE’s strategy is not to compete with the standard chip manufacturers, but to use the ASIC and FPGA technologies for `system on chip’ design, which demands standards like I2C with customer specific user functions.

Serial Controller Interface

Overview

Key Features

- I2C-Compatible

- Slave Function

- 7-Bit Slave ID Address

- Automatic Incremented Address Pointer(AP)

- AP Initialization by transferring Word Address on I2C Bus

- Message Acknowledgement

- Customizable for Special Requirements

Benefits

- iniSCI is modular structured into a BitSync bus interface, receiver, transmitter, and framer modules. This modular structure facilitates an understanding of the core’s functionality, thus simplifying customization.

Block Diagram

Deliverables

- VHDL or Verilog RTL Source Code

- Functional Testbench

- Synthesys Script

- Data Sheet

- User Guide

- Hotline Support by means of phone, fax and e-mail

Technical Specifications

Foundry, Node

Technology independent

Maturity

Proven in ASIC and FPGA Technologies

Availability

now

Related IPs

- Expanded Serial Peripheral Interface (xSPI)Master Controller

- Expanded Serial Peripheral Interface (xSPI) Slave Controller

- I2S/TDM Serial Audio Interface with Asynchronous Sample Rate Conversion

- Synchronous Serial Interface Controller

- Express Serial Peripheral Interface IP Core

- MIPI DSI-2 host/device controllers for high-speed serial interface between application processor and displays