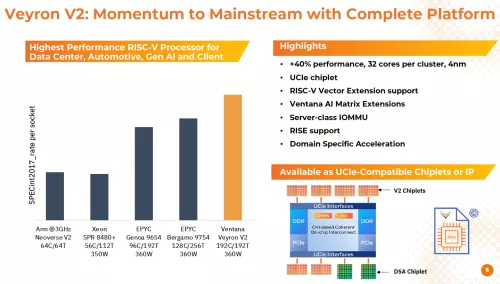

The RISC-V high performance CPU is targeted at data center, edge, and other general computing applications. The configurable CPU cluster can be integrated as IP within an SoC, delivered as an optimized compute chiplet, or within an ASSP/CSSP SiP standard product.

Veyron is a server-class CPU, meeting all the requirements to run virtualized cloud-native workloads and adhering to robust data center requirements. The V1 IP portfolio includes key RISC-V system IP components such as an IOMMU, and its interface is compliant to common AMBA protocol standards, such that complete high performance system solutions can be easily integrated with available third-party IP.