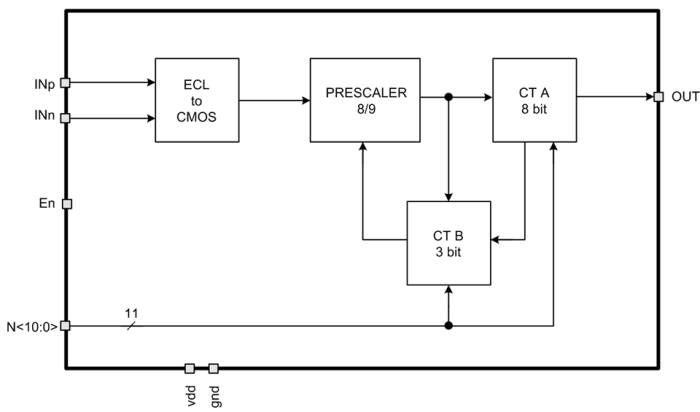

The CMOS PLL high-frequency divider consists of the converter of a differential input signal to an unipolar signal with a supply voltage peak-to-peak, a prescaler with variable dividing ratio 8/9 and two binary decade counters.

The block is fabricated on TCMS BiCMOS 0.18 um technology.

Programmable CMOS PLL high-frequency divider

Overview

Key Features

- TCMS BiCMOS 0.18 um

- Wide range of dividing ratio (56…2047)

- Low current consumption

- Compact structure

- Wide range of operating frequency - up to 5 GHz

- Portable to other technologies (upon request)

Block Diagram

Applications

- PLL frequency synthesizer

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

Programmable CMOS PLL high-frequency divider

Vendor

Vendor Name

Foundry, Node

TSMC BiCMOS SiGe 180 nm

Maturity

Silicon proven

Availability

Now

TSMC

Silicon Proven:

180nm

Related IPs

- Programmable CMOS PLL high-frequency divider

- Programmable CMOS PLL high-frequency divider

- Programmable 9-bit CMOS frequency divider (2…511 dividing ratio)

- Programmable CMOS HF divider (16…4095 dividing ratio)

- Programmable CMOS frequency divider (32...16383 dividing ratio)

- Programmable 9-bit CMOS low-frequency divider (5...511 dividing ratio)