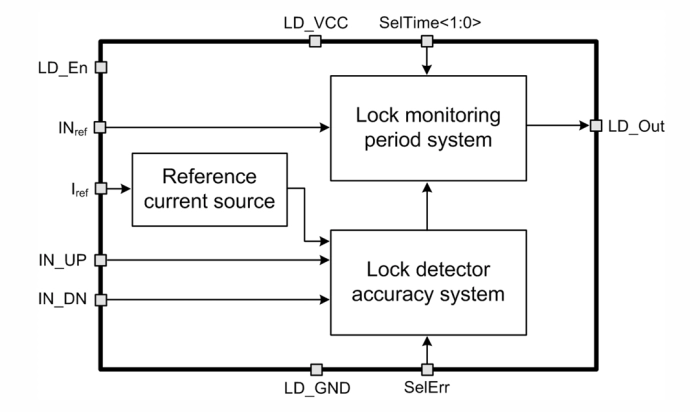

The lock detector monitors the current status of PLL by comparing the phase difference of VCO divided signal and reference oscillator signal with required value. It is available to set the lock monitoring period and the lock detector accuracy (5.5...12 ns).

PLL lock detector with low current consumption and high accuracy

Overview

Key Features

- TSMC SiGe 0.18 um

- Low current consumption

- High accuracy

- Portable to other technologies (upon request)

Block Diagram

Applications

- Phase-locked loop synthesizer

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

PLL lock detector with low current consumption and high accuracy

Vendor

Vendor Name

Foundry, Node

TSMC SiGe 0.18 um

Maturity

Silicon proven

Availability

Now

TSMC

Silicon Proven:

180nm

Related IPs

- PLL lock detector with low current consumption and high accuracy

- PLL Lock detector with low current consumption and high accuracy

- PLL Lock detector with low current consumption and high accuracy

- PLL Lock detector with low current consumption and high accuracy

- Multi-constellation and Multi-frequency Correlators Soft GNSS IP for high sensitivity and high accuracy GNSS receivers

- High-performance microcontroller core with a 12-stage dual-issue out-of-order pipeline and a high performance FPU