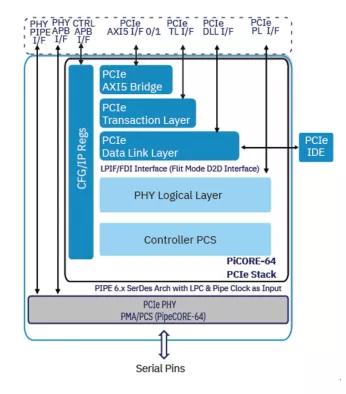

The Controller IP is customer configurable and supports PCIe 6.x/PCIe5.x/PCIe4.x/PCIe3.x/ PCIe2.x/PCIe1.x Specifications. The Controller IP support lane widths from x1 to x16.

PCIe 6.x / PCIe5.x / PCIe4.x / PCIe3.x / PCIe2.x / PCIe1.x Controller

Overview

Key Features

- Implements PCIe 6.0 Specification at 64 GT/s

- Parallel Multiple TLP/DLLP processing engine for best performance, throughput, and latency

- Designed for easy integration with Alphawave PipeCORE™ PCIe PHY IP

- Key IP features configurable to optimize IP for exact application requirements

Benefits

- Configurability.

- The IP core can be configured to support two key modes: Device Dual Mode (“Root Port” or “Endpoint”) and Switch Dual Mode (“Switch Downstream Port” or “Switch Upstream Port”). This allows users to use the IP in a wide variety of PCIe applications.

- Verification.

- The IP has been verified against leading PCIe VIP and available compliance test suite. This IP is proven in silicon using an Alphawave PHY IP on a Test chip. The controller IP has also been verified in Emulation as well as on an FPGA using Xilinx PHY interoperating with an Intel PCIe Motherboard.

- Customizability.

- To easily optimize the PCIe IP for the exact application requirements, the IP comes with an easy-to-use, graphical IP Configuration wizard that allows users to enable, disable, or tune features in the IP, or to add or remove optional ECNs (Engineering Change Note). The IP supports multiple data path widths designed for optimal area when used for narrower lane widths.

Block Diagram