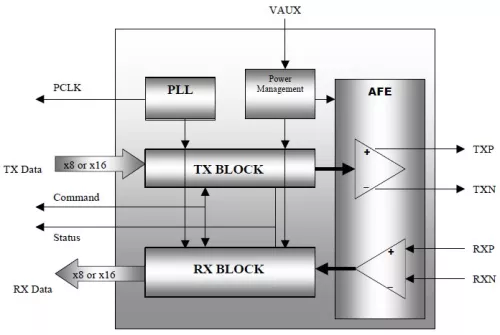

SMS5000 is a fully integrated CMOS transceiver that handles the full Physical Layer PCI Express protocol and signaling. It contains all necessary AFE (Analog Front End), Clock synthesis, Clock Recovery, Serializer, De-serializer, Comma detect for 8B/10B encoded data and frame alignment functionalities. Digital controller interface is realized with a 8-bit parallel operation (Optional 16-bit Interface) that allows use of 250 MHz reference Clock. The transceiver includes Receiver Detection, Beacon Generation, Beacon Detection and Signal Detect capability compliant with PCI Express Specification requirements and provides Short Circuit Protection to ground for outputs. SMS5000 also includes calibrated Transmitter and Receiver Termination Resistors compliant with the requirements of the PCI Express Base 1.0a Specification.

SMS5000 does not require any external Loop filter capacitor(s) for clock Synthesis PLL or Clock recovery circuitry making it immune to PCB related noise typically encountered, and provides a completely integrated solution.

PCI Express PHY serial link PIPE Transceiver IP cell/hard macro

Overview

Key Features

- Supports 2.5Gb/s serial data rate

- Utilizes 8-bit or 16-bit parallel interface to transmit and receive PCI Express data

- Full Support for Auxiliary Power (Vaux) for Energy aware systems like Multi-Port Host Controllers

- Data and clock recovery from serial stream on the PCI Express bus

- Supports direct disparity control for use in transmitting compliance pattern

- 8b/10b encode/decode and error indication

- Receiver detection

- De-emphasis at Transmit

- Electrical Idle Generation & Detection

- Lane Polarity Inversion Support

- Loop-back Support

- Spread Spectrum Clock Support

- Embedded Bit Error Rate Testing Through PBRS generation and detection

- Short Circuit Protection

- Scrambling Disable Feature

- Beacon transmission and detection

- Direct Disparity Control Support for use in transmitting compliance pattern

- Full low cost, low power CMOS Implementation

- Modular architecture supports 1,2,4,8,16 Lane applications

- Optimized, Proprietary architecture yields very small silicon area

- Hot Swap, Hot Plug Support

Block Diagram

Deliverables

- GDS2

- Full behavioral model

- test vectors

- test bench for integration testing

- verification environment

- characterization and testing documents

Technical Specifications

Foundry, Node

0.18u and below

Maturity

Please contact the provider for test chip availability

Availability

now

TSMC

Pre-Silicon:

130nm

,

130nm

G

,

150nm

G

,

180nm

G

UMC

Pre-Silicon:

130nm

,

150nm

,

180nm

Related IPs

- Spartan-3 LogiCORE Endpoint PIPE for PCI Express (PCIe)

- PCI Express Gen3 / SATA3 SERDES PHY on Samsung 28FDSOI

- PCI Express Gen3 SERDES PHY on Samsung 28LPP

- PCI Express Gen3 SERDES PHY on Samsung 7LPP

- PCI Express Gen3 SERDES PHY on TSMC CLN40G

- PCI Express Gen3/4 Enterprise Class SERDES PHY on Samsung 14LPP