Combination MIPI CPHY-DPHY Analog Interface

The MIPI C-PHY V1.0 improves throughput over a bandwidth limited channel, allowing more data without increased signaling clock. It is intended to be used for camera interface (CSI-2 v1.3) and display interface (DSI v1.2). The signaling interface uses a 3-phase transceiver that encodes 3 bit symbols over 3 wires. This is different that the two-wire differential “lane” used in D-PHY.

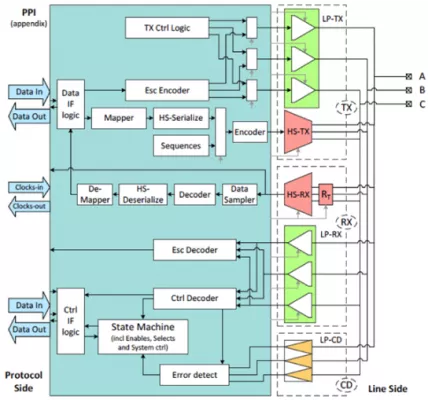

C-PHY was designed to coexist on the same IC pins as D-PHY so that dual-mode devices can be developed with low power signaling similar to DPHY. Arasan’s CPHY-DPHY combination provides a 3 channel C-PHY v1.0 and a four lane D-PHY v1.2 in a single IP core. This allows a seamless implementation and allowing interface to D-PHY based sensors or C-PHY based sensors.

Symbol encoding effectively transfers 2.286 bits per symbol compared to 1.0 bits per lane for D-PHY. The first version of C-PHY (v1.0) operates at 2.5GHz, same as the D-PHY V1.2.

A four lane D-PHY V1.2 provides 10Gbps which enables:

- 4K video at 30fps

- 1080p at 120fps

A 3 channel C-PHY provides 17Gbps which enables:

- 4K video at 60fps

- 1080p at 240fps (for cool slow-motion videos)