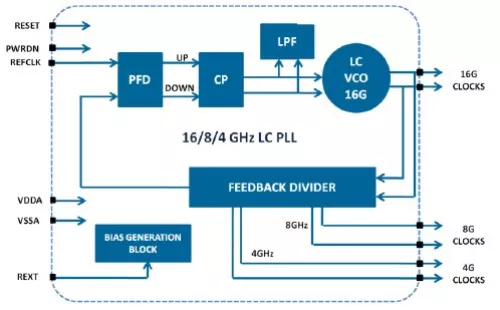

Terminus Circuits offers an Analog Phase Locked Loop which is a LC oscillator-based integer-N PLL IP powered at 900 mV. The PLL operates with input reference frequency of 100 MHz makes it applicable for multi-standard clocking applications. The output frequency is 16 GHz, 8 GHz and 4GHz with quadrature outputs for 8GHz and 4GHz.

A reset sequence is designed to achieve phase lock on power up or mode change.

The PLL needs a dedicated power supply to reduce the effect of supply noise on it.

The frequency output is applicable for multiple protocols.

High Speed Low Jitter 16GHz Output LC PLL

Overview

Key Features

- Type II, 3rd order low Jitter PLL

- Auto calibration for process and temperature (USP)

- Programmable frequency using CSR registers

- 16 GHz, 8GHz and 4GHz with quadrature clocks

- Operating temperature -40oC to 125 oC

- Standby / power down mode

- Low silicon surface

Benefits

- LC Oscillator based VCO

- Low area

- Works in two modes - Normal and Power Down

Block Diagram

Applications

- Clock multiplication

- Clock for High speed generators for SerDes PHY

- Clock Recovery

Deliverables

- GDS II Layouts

- LEF abstracts

- CDL netlists

- Liberty timings

- Verilog description

- A full datasheet

- An integration note

Technical Specifications

Short description

High Speed Low Jitter 16GHz Output LC PLL

Vendor

Vendor Name

Foundry, Node

TSMC 28nm, GF 28nm, Samsung 28nm

Maturity

Silicon validated, Pre-silicon

Availability

Now

TSMC

Pre-Silicon:

90nm

LP

Related IPs

- PCIe Gen4/5/6 Class Low Jitter LC PLL on TSMC CLN2P

- PCIe Gen4/5/6 Class Low Jitter LC PLL on TSMC CLN3E

- PCIe Gen4/5/6 Class Low Jitter LC PLL on TSMC CLN3P-CLN3X

- PCIe Gen4/5/6 Class Low Jitter LC PLL on TSMC CLN6FF

- PCIe Gen4/5/6 Class Low Jitter LC PLL on TSMC CLN7FF

- High speed low latency AES-GCM pipeline, 100Gbps