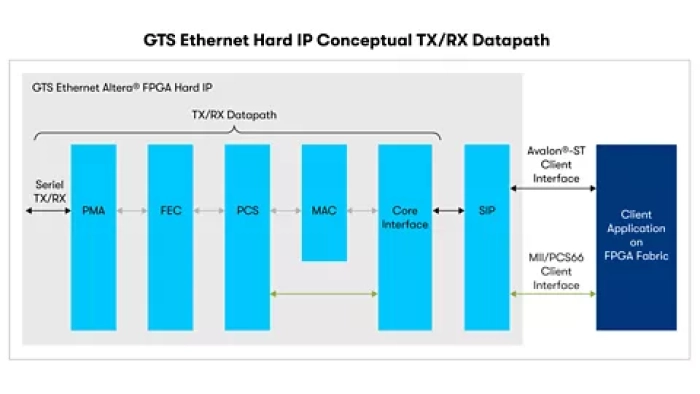

Ethernet is ubiquitous across many markets and applications. The GTS Ethernet Intel FPGA Hard IP (EHIP) allows fast, flexible, and high-performance Ethernet implementation with minimal FPGA resource utilization. The EHIP includes a configurable, hardened protocol stack for Ethernet, compatible with the IEEE 802.3-2018 - IEEE Standard for Ethernet and the 25G/50G Ethernet Specification from the 25 Gigabit Ethernet Consortium.

GTS Ethernet Hard IP Connects an Increasing Number of Devices

Agilex™ 5 devices serve a broad range of applications that require high performance, lower power, and smaller form factors. These characteristics make them ideal for midrange FPGA applications across the edge and core including:

- Wireless and wireline communications

- Video and broadcast equipment

- Industrial applications

- Test and measurement products

- Medical electronics

- Data center

- Defense applications

The majority of the applications listed above utilize Ethernet connectivity and can leverage the EHIP to help accelerate their designs.

Features

|

Features |

Description |

|---|---|

|

Ethernet Rate/PMA combination [Data Rate]-[Number of PMA] |

|

|

PMA Type |

ETH MAC and OTM support on CH3 and CH2 per bank. All channels support PCS Direct and FlexE mode. |

|

Flexible Configuration |

|

|

Client interface |

|

|

Forward error correction (FEC) |

|

|

Precision Timing and Link Training |

|