Comprehensive hardware and software TSN capable solution designed for automotive applications

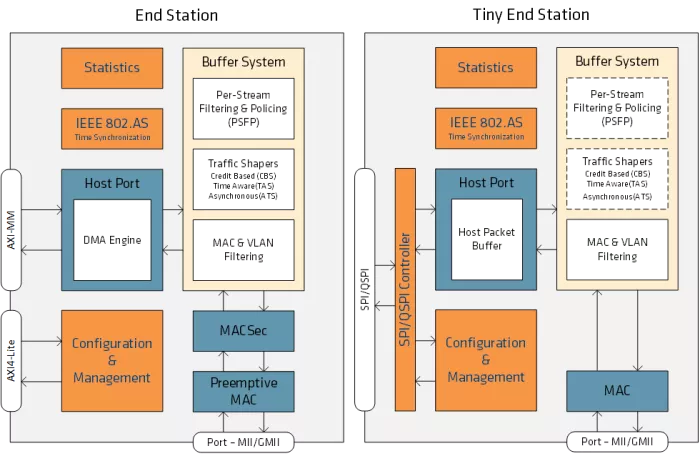

The Ethernet Tiny TSN Endstation Controller IP is targeted at simple sensor and actuator automotive applications like climate control, lighting, and locks. It provides connectivity to the in-vehicle TSN Ethernet and precise time synchronization. The version supports 10M/100M half and full-duplex operation and utilize standard MII/RMII and MDIO interfaces to communicate with Ethernet Physical layer devices. Its configuration and status register are accessible via a Quad Serial Peripheral Interface (QSPI) serial bus

It also implements a host buffer to store packets transferred between the network interface and the external microcontroller. The packets in the host buffer are accessed by the external microcontroller via the same QSPI used for configuration and status.

The Ethernet TSN Endstation Controller IP family from is a comprehensive hardware and software solution for automotive applications. The solution implements Timing & Synchronization (802.1AS), Multiple types of Traffic Shaping (802.1Qav, 802.1Qby, 802.1Qcr), Frame preemption (802.1Qbu), Frame replication & elimination (802.1CB), Steam filtering & policing (802.1Qci), and optional MACsec encryption/decryption (802.1AE).

The solution is designed to provide high-precision time synchronization and accurate traffic scheduling. It supports up to 8 traffic classes, each with a dedicated queue for all ports. It is available in two versions: Ethernet TSN Endstation Controller IP and Ethernet Tiny TSN Endstation Controller IP.

Both versions of the Ethernet TSN Endstation controller IP include a comprehensive software package with device drivers for several operating systems, a software stack for 802.1AS and a complete demonstration system based on Linux.

The solution is available as technology independent RTL source code (System Verilog) or encrypted netlist for ASIC and FPGA implementations. Furthermore, FPGA based hardware platforms are available for evaluation and prototyping.