The Ethernet MII/RMII/GMII/RGMI Synthesizable Transactor verifies Ethernet interfaces. Ethernet is build on top of it to make it robust. Ethernet MII/RMII/GMII/RGMI Synthesizable Transactor provides a smart way to verify the Ethernet component of a SOC or a ASIC in Emulator or FPGA platform. Ethernet MII/RMII/GMII/RGMI Synthesizable Transactor is developed by experts in networking, who have developed networking products in companies like Intel, Cortina-Systems, Emulex, Cisco. We know what it takes to verify a networking product.

Ethernet MII/RMII/GMII/RGMII Synthesizable Transactor

Overview

Key Features

- Supports Full MII/RMII/GMII/RGMII TX/RX functionality

- Supports Mac control and data frames support

- Ability to generate VLAN tagged and Priority tagged frames

- Supports Pause frame detection and generation

- Supports Jumbo frames

- Supports Under and oversize frame

- Supports 1G:

- Supports GMII

- Supports TBI (i.e Output of 8b/10b PCS)

- Supports SGMII/SGMII_TBI as per specification 1.8

- Supports RGMII/RTBI as per specification 2.0

- Supports 1000Base-KX

- Supports clause 73 backplane auto-negotiation for 1000Base-KX

- Supports clause 37 auto-negotiation

- Supports full duplex and half duplex of operation

- Supports all types of TX and RX errors insertion/detection at each layer

- Supports Under and oversize frame

- CRC errors

- Framing errors

- Pause frame errors

- Disparity and Auto-negotiation errors

- Invalid code group insertion

- Invalid /K/ characters insertion

- Lane Skew insertion

- Invalid AN sequence error insertion

- Missing /K/ characters for packet boundaries

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

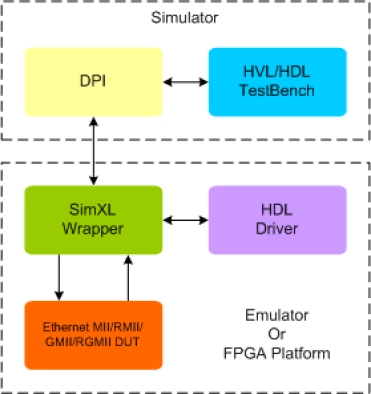

Block Diagram

Deliverables

- Synthesizable transactors

- Complete regression suite containing all the Ethernet testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation contains User's Guide and Release notes

Technical Specifications

Short description

Ethernet MII/RMII/GMII/RGMII Synthesizable Transactor

Vendor

Vendor Name