A highly scalable and silicon agnostic implementation of the eCPRI standard

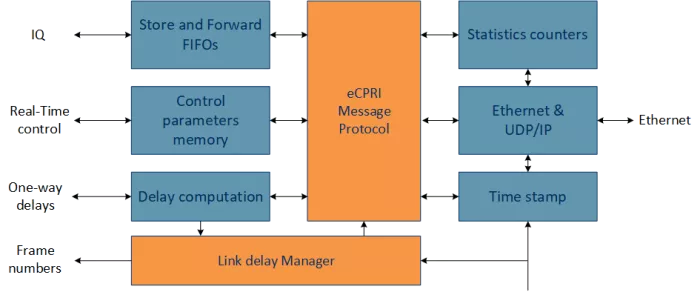

The eCPRI core is a highly scalable and silicon-agnostic implementation of the eCPRI standard targeting any ASIC, FPGA or ASSP technologies. The eCPRI implementation builds on long-time experience designing CPRI and Radio-Over-Ethernet solutions for fronthaul and delivers a flexible engine that is prepared for tight integration with software applications.

The IP is designed to meet or exceed the requirements of radio systems, baseband systems, fronthaul switches or advanced test systems. The speed-optimized core can handle any solutions reaching from the “small footprint” to the most complex applications running 25 Gbps. The IP can dynamically be configured to handle wireless multi-mode radio systems enabling high-performance throughputs required by 4G and 5G wireless solutions.