At the heart of the Unity platform is the ‘Unity’ CPU core. The CPU is validated in TSMC’s 28nm process and is configurable for multiple performance levels.

CPU - Unrivalled scalability for heterogeneous design

Overview

Key Features

- Operating frequency:

- Up to 2.5 GHz, based on process technology and optimization selection

- Out-of-order pipeline:

- Increased instruction throughput; 256 in-flight instruction capable

- Distributed instruction decoding:

- Optimizes design for power and performance through localized instruction decoding

- Distributed register files:

- Reduces register rename complexity and register file ports

- General Purpose, F-Point, Address, and Branch Jump Target register files

- Distributed register renaming:

- Localized to each functional unit for register files owned by the functional unit to achieve higher instruction throughput and simplify register rename logic

- Capable of up to 63 physical registers per unit

- Instruction prefetch structure:

- Reduces instruction dispatch time

- Branch Predictor:

- Reduces memory access times / improves execution performance

- 2048 2-bit saturating branch predictor

- L0 and L1 I-caches:

- Facilitate fast instruction fetch; configurable to user requirements

- L1 D-cache:

- Enables fast memory accesses; configurable to user requirements

- Dynamically Configurable L2 unified code and data cache:

- Enables fast memory accesses

- Memory Coherency:

- Maintains consistent data across memories/caches; capable at all memory subsystems

- Privilege Levels:

- Three access levels are provided with increasing access to system resources

- Ease implementation of hypervisors and virtualization; enforce isolation between processes

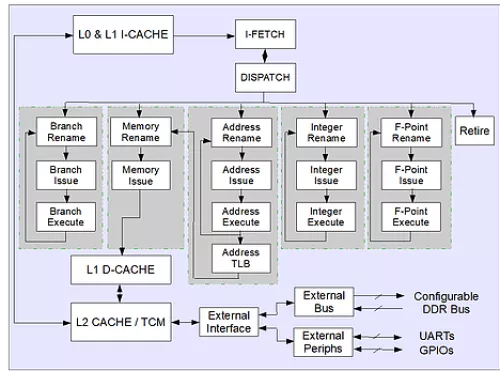

Block Diagram

Technical Specifications

Short description

CPU - Unrivalled scalability for heterogeneous design

Vendor

Vendor Name

Related IPs

- Compact High-Speed 64-bit CPU for Real-time and Linux Applications

- Compact High-Speed 32-bit CPU for Real-time and Linux Applications

- LDO for CPU Cores on TSMC CLN2P

- Self-contained cryptographic subsystem designed for PQC + classical, minimal integration effort, with SCA protection

- Scalable RISC-V CPUs for Data Center, Automotive, and Intelligent Edge

- Stallable pipeline stage with protocol for multiway pipeline fork and join capability