Camera Link Interface

The Camera Link® IP Core is a high-speed LVDS transmitter / receiver pair that conforms to the standard Camera Link protocol orig…

Overview

The Camera Link® IP Core is a high-speed LVDS transmitter / receiver pair that conforms to the standard Camera Link protocol originally developed by National Semiconductor Corp®.

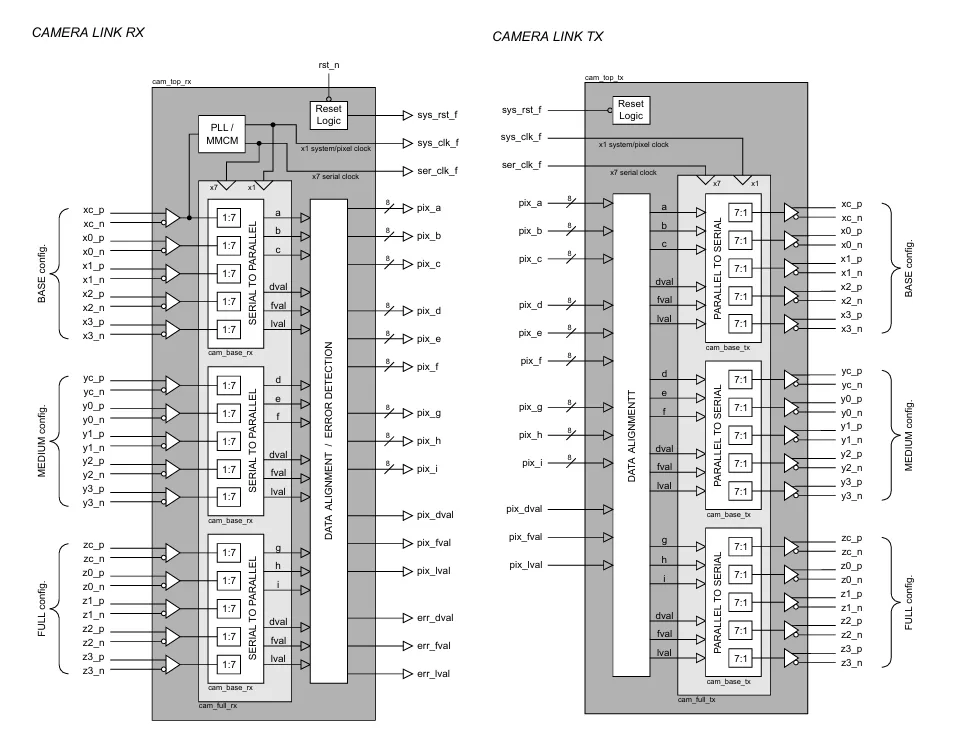

The design is comprised of an independent transmitter and receiver that may be implemented separately or together as a single transceiver unit. The IP Core may be used in either the BASE, MEDIUM or FULL configurations as defined in the Camera Link specification.

In general, each data lane can support around 500 Mbps (max) per LVDS lane on basic FPGA and SoC devices. This gives a typical throughput of around 2 Gbps over the 4 data lanes (BASE), 4 Gbps over 8 lanes (MEDIUM) or 6 Gbps over 12 lanes (FULL). However, the maximum data rate attained will be dependent on a wide range of factors such as: cable type, cable length, PCB board layout and also the choice of target device.

Key features

- Technology independent soft IP Core for FPGA, SoC and ASIC

- Supplied as human readable VHDL (or Verilog) source code

- Separate Camera Link® Receiver (frame-grabber) and Camera Link® Transmitter (camera) IP Cores

- Supports BASE, MEDIUM and FULL configurations of the Camera Link specification

- Fully configurable clocking via PLL using the clock management resources available on the target device

- Error checking for data misalignment at the Camera Link receiver

- Supports a parallel clock of ~70 MHz or ~500 Mbps / lane on basic FPGAs and SoCs. Higher data rates supported on higher-end devices

- No special interface circuitry required. Connects directly to the standard LVDS I/O resources available on common FPGA and SoC devices

Block Diagram

Applications

- Real-time / low-latency video interfaces on low-cost devices

- Data streaming interfaces over cable or twisted pair

- General purpose LVDS / SERDES applications

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Transport IP core

Introduction to Embedded DisplayPort (eDP) version 1.5

Enabling High Performance SoCs Through Multi-Die Re-use

An HDTV SoC Based on a Mixed Circuit-Switched / NoC Interconnect Architecture (STBus/VSTNoC)

Steps for Delivering Multimedia Over 5 GHz WLANs

Tutorial: The H.264 Scalable Video Codec (SVC)

Frequently asked questions about Video Transport IP cores

What is Camera Link Interface?

Camera Link Interface is a Video Transport IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Video Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.