The AES MPEG-TS interface core allows to encrypt or decrypt MPEG-TS stream using the MVD AES encryption core.

•The AES interface module processes the incoming stream and determines the packets that must be encrypted or decrypted according to the programmed configuration.

•The AES Interface module controls the AES core by sending it adapted Key and 128-bit Words to process.

•The module extracts words from MPEG TS interface and replaced them by AES processed words.

•Output packets are modified according to the process mode used.

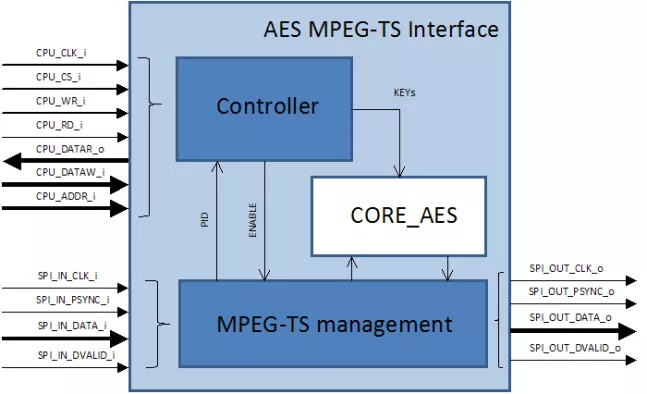

AES MPEG-TS Interface

Overview

Key Features

- Drop-in module for Spartan®-6, Virtex®-6, Artix™-7, Kintex™-7 and Virtex®-7 FPGAs

- 135MHz Single clock

- DVB/ATSC compliant

- Manage odd/even key encryption.

- Selection of Encryption Key Size between 128, 192 and 256 bits

- Selection of any 8192 possibles PIDs(user must take care to not encrypt PSI/SI or PSIP tables)

- Automatically update encryption flags of MPEG-TS packet header

- Supports 188, 204, 208 bytes packet input

- Supports Data Packet or Data Burst format

- AES MPEG-TS Interface does not include ECM/EMM packets insertion nor CAT modification (see remultiplexer core option for these features)

- Full synthesizable RTL VHDL design (not delivered) for easy customization

- Design delivered as Netlist

Block Diagram

Applications

- The AES-MPEG-TS interface core can be used to encrypt MPEG-TS stream in order to broadcast it in a basic local network and gives access to the contents to only authorized user.

Deliverables

- Datasheet

- Netlist for core generation

- VHDL top file

- VHDL source code : can be delivered as an option under NDA and other specific clauses

Technical Specifications

Short description

AES MPEG-TS Interface

Vendor

Vendor Name