The OT3128rj is a flexible clock multiplier PLL function with a wide range of input and output frequencies and is designed for the ams (Austriamicrosystems) aC18 or aH18 0.18µ digital or high voltage CMOS processes. The design features an advanced multi-stage balanced VCO for the exceptional cycle to cycle jitter performance.

600MHz General Purpose PLL

Overview

Key Features

- Wide range M integer divider. (See ot3122 for M, N, and P dividers)

- 250MHz – 600MHz output frequency range.

- Comparable frequency range 8MHz – 50MHz.

- 18pS RMS cycle to cycle jitter at 600MHz.

- Lock-detect function.

- Bypass function.

- Well defined startup behavior.

- -40°C to 140°C temperature operation.

- Available divider selection program.

- Small cell area: 0.04mm2 in 0.18µ CMOS.

- 2mW typical power dissipation.

- 1.8V digital and analog supplies.

- 0.18µ CMOS process compatibility.

- Only 1.8V transistors are used in the design.

- Silicon proven.

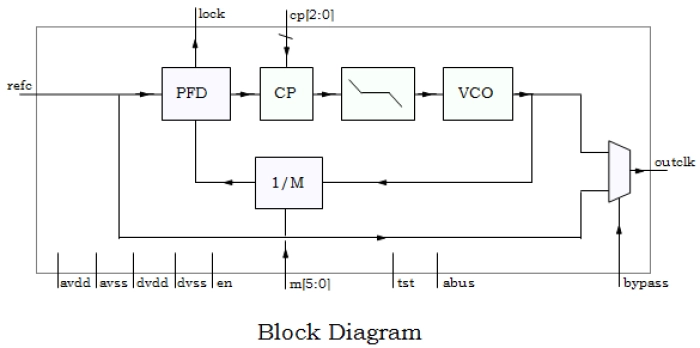

Block Diagram

Technical Specifications

Short description

600MHz General Purpose PLL

Vendor

Vendor Name