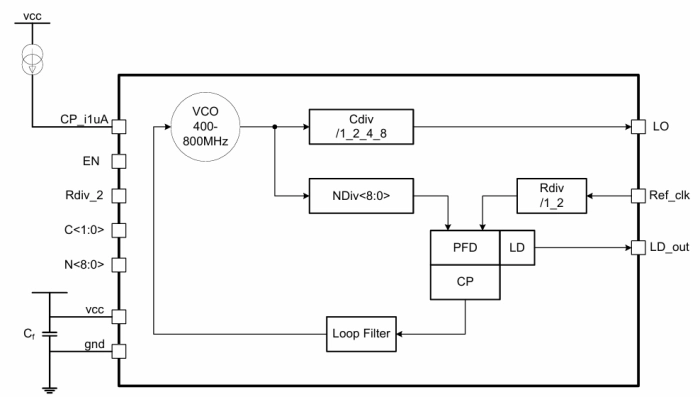

The synthesizer forms clock signal with frequency from 50 to 800 MHz. It consists of the ring VCO with frequency from 400 to 800 MHz, a programmable feedback divider, a low noise digital phase noise detector (PFD), a precision charge pump (CP) with internal loop filter and programmable clock divider to obtain a required output frequency. Output frequency is calculated by formula: FLO = (Fref*N)/(R*C). Power supply is 1.2V. Output signal is CMOS compatible.

50 - 800 MHz phase-locked loop

Overview

Key Features

- TSMC CMOS 65 nm

- Output frequency from 50 to 800 MHz

- Reference frequency from 4 to 30 MHz

- Power supply 1.2 V

- CMOS output

- Portable to other technologies (upon request)

Block Diagram

Applications

- Digital circuit clocking

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

50 - 800 MHz phase-locked loop

Vendor

Vendor Name

Foundry, Node

TSMC CMOS 65 nm

Maturity

Silicon proven

Availability

Now

TSMC

Silicon Proven:

65nm

G