D/AVE NX is the latest and most powerful addition to the D/AVE family of rendering cores. It is the first IP to bring 3D graphics OpenGL ES 2.0 rendering (with some ES 3.0 / 3.1 extensions) to the FPGA and SoC world and – with offline-shader compilers – even into MCUs or low-end MPUs with small amounts of memory and bare-metal or RTOS operation systems. Targeted for graphics applications on displays up to 4K x 4K resolution in the Industrial, Medical, Military, Avionics, Automotive and Consumer markets, D/AVE NX is designed to meet the sweet spot of performance and footprint bringing full 3D graphics even down to MCU class devices and into safety critical applications.

By enabling the use of programmable shaders even on small devices, high quality 2D and full 3D applications can be realized using the D/AVE NX core. Support for industry standard APIs like OpenGL ES 2.0 allows for rapid development of high-end user interfaces by leveraging common GUI frameworks like LVGL, Qt or SCADE and makes new, future proof implementations possible.

D/AVE NX can scale easily to fit exactly into the resource / performance sweet spot for a particular application. Entire device families can be equipped with differently scaled variants of the core, making all of them fully software compatible. A single unified software stack and the guarantee to produce exactly the same visual result (at different speeds) allows saving significant development resources.

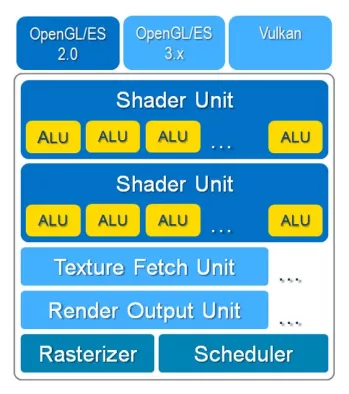

D/AVE NX is highly efficient as the internal multi-level scheduler can maximize the utilization of every HW element even better than the fixed function pipeline of the successful D/AVE cores could. Scheduling also does not have to be precomputed in the compiler, simplifying the compiler and driver architecture considerably.