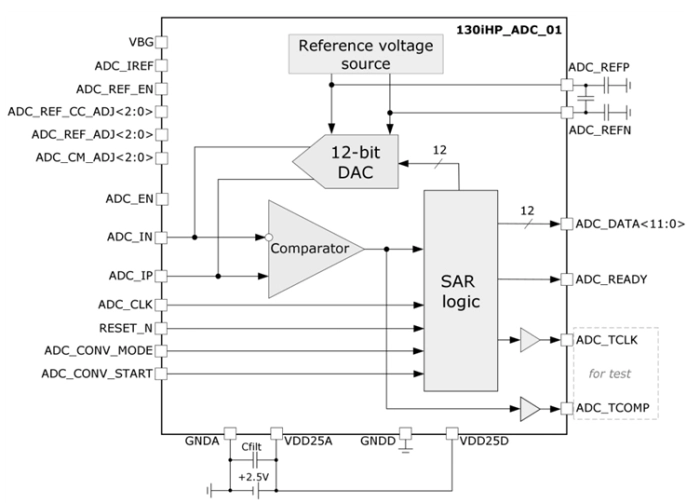

130iHP_ADC_01 employs high-performance successive approximation architecture. The ADC operates with sampling rate from 1 to 10 kSPS and input clock from 14 to 140 kHz. The block has differential input and can operate in two modes: single measurement or continuous measurement. The ADC supports standby mode and features low power consumption, compact area.

12-bit 1-channel 1 to 10 kSPS SAR ADC

Overview

Key Features

- Resolution 12-bit

- Sample rate 1-10 kSPS

- Low power dissipation: 1 mW at 10 kSPS

- Separate power supplies for digital (2.5 V) and analog (2.5 V) parts

- iHP SiGe BiCMOS 0.13um technology

Block Diagram

Applications

- On chip voltage measurement

- Receivers

- Measurement equipment

- Medical equipment

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

12-bit 1-channel 1 to 10 kSPS SAR ADC

Vendor

Vendor Name

Foundry, Node

iHP SiGe BiCMOS 130nm

Maturity

Silicon proven

Availability

Now