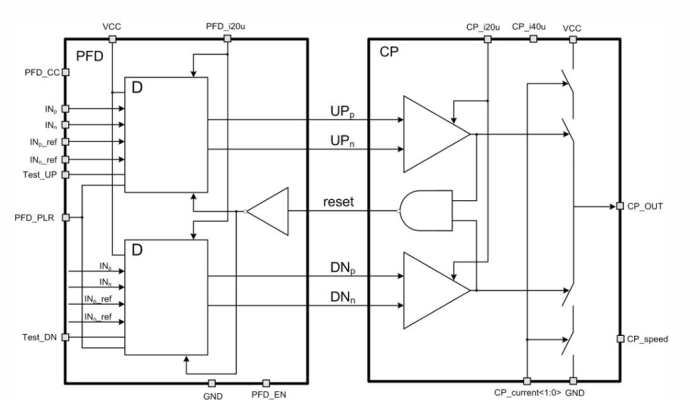

Phase-frequency detector (PFD) forms a control signal for VCO tuning. PFD compares phases of a divided VCO signal and a divided reference oscillator signal and detects phase difference. Charge pump generates pulses for the loop filter.

Reference frequency 1…20 MHz.

Output current is 0.4...6.4 mA.

1 to 20 MHz Phase-frequency detector and charge pump

Overview

Key Features

- AMS BiCMOS 0.35 um

- Input signals with low amplitude

- Low disbalance of output current

- Portable to other technologies (upon request)

Block Diagram

Applications

- Phase-locked loop synthesizer

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

1 to 20 MHz Phase-frequency detector and charge pump

Vendor

Vendor Name

Foundry, Node

AMS BiCMOS 0.35 um

Maturity

Silicon proven

Availability

Now

Related IPs

- 0.1 to 25 MHz Phase-frequency detector with charge pump

- 24.84 MHz Phase-frequency detector with charge pump (input amplitude 150…210 mV)

- PLL 24.84 MHz phase-frequency detector with charge pump

- 24.84 MHz Phase-frequency detector with charge pump

- 24.84 MHz phase-frequency detector with charge pump

- PLL CMOS phase-frequency detector with ECL charge pump