GUC 宣布 CSP 資料中心採用 HBM3E IP

å°ç£æ°ç«¹ – 2024å¹´09æ24æ¥ – å

é² ASIC é å°å» ååµæé»å (GUC) å¾é«è宣å¸ï¼å

¶ 3 å¥ç±³ HBM3E æ§å¶å¨å實é«å±¤ IP å·²ç²é å

æ¥ççé²ç«¯æåä¾æå (CSP) åå¤å®¶é«æéç® (HPC) 解決æ¹æ¡ä¾æåææ¡ç¨ãé款å°ç«¯ ASIC é è¨å°æ¼ä»å¹´æµçï¼ä¸¦å°æ¡ç¨ææ°ç 9.2Gbps HBM3E è¨æ¶é«æè¡ã

åµæé»åç HBM3E æ§å¶å¨å PHY IP å·²è¢«è¨±å¤ AI å

¬å¸æ¡ç¨ï¼åµæé»åä¹ç©æ¥µè HBM ä¾æåï¼å¦ç¾å

ï¼åä½ï¼çºä¸ä¸ä»£ AI ASIC éç¼ HBM4 IPã

åµæé»å HBM3E IP 亮é»ï¼

- ééå°ç©é»å é²è£½ç¨æè¡çé©èï¼å°ç©é» N7/N6ãN5/N4PãN3E/N3P 製ç¨ã

- ééææä¸»æµ HBM3 å» åçç½é©è

- å¨å°ç©é» CoWoS-S å CoWoS-R æè¡ä¸åééç½é©èï¼åµæé»åçº TSMC CoWoS-S è¨è¨ eDTCè CoWoS-R è¨è¨ IPDï¼ä»¥å¯¦ç¾æä½³é»æºå®æ´æ§ã

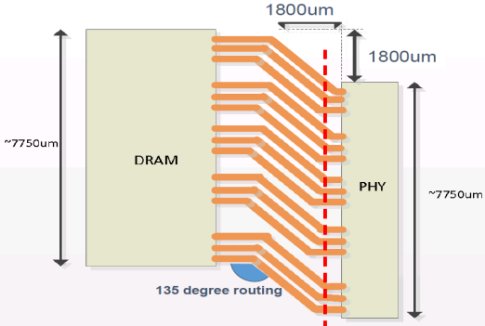

- é«éä¸ä»å±¤(Interposer)ä½ç·ï¼å°å©ä¸ä»å±¤ä½å±ï¼æ¢æ¯æ´å · Y 軸å移çè§åº¦ä½ç·ï¼åè½ä¿ææä½³çä¿¡èå®æ´æ§åé»æºå®æ´æ§ã

- å §å»ºå°æ¶çäºé£ç£æ§è§£æ±ºæ¹æ¡ï¼GUC è proteanTecs åä½ï¼å°å°æ¶çäºé£ç£è¦å¨æ´åå° HBM PHY ä¸ãæ¤åè½å¢å¼·äºå°æ¶ççå¯è§å¯æ§åå¯é æ§ã

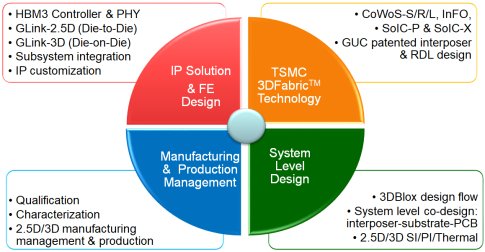

- å®æ´ç2.5/3Då¤æ¶çè¨è¨æåï¼åµæé»åå¯çº HBM CoWoS ASIC å¹³å°è¨è¨æä¾å®æ´ç 2.5D è 3D æåçé¸é ã

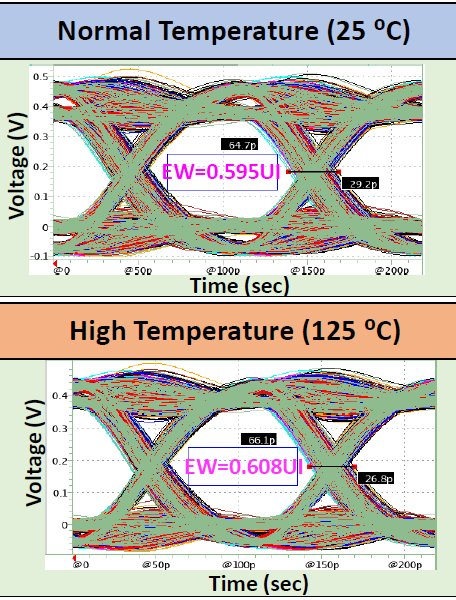

HBM3E 9.2G ç¼å (Eye Diagram)

ä¸ä»å±¤ (Interposer) è§åº¦ä½ç·

åµæé»åæä¾2.5D/3D ASICè¨è¨å ¨æ¹ä½æå

åµæé»åèç¾å ä¹éçåä½èæï¼åµæé»åçHBM3E IP èç¾å HBM3E å¯ä»¥å¨ CoWoS-S å CoWoS-R æè¡ä¸å¯¦ç¾ 9.2Gbpsãåµæé»å測試æ¶ççç½çµæ顯示ï¼é¤äºé»æºå®æ´æ§ (PI) èä¿¡èå®æ´æ§ (SI) çµæééèé©ï¼å¨ä¸å溫度åé»å£è§è½ä¸ä¹åå¾åªç°çç¼åééãæ¤å¤ï¼åµæé»åç IP èç¾å ç HBM3E æåºåæ¸æ´åæå¯å±ç¾æ´ææçå¯æµæå©ç¨çï¼é²ä¸æ¥å¢å¼·æ´é«ç³»çµ±æè½ã

ãæåå¾é«èçå°æåç HBM3E æ§å¶å¨å PHY IP æ´åå° CSP å HPC ASIC ä¸ãã åµæé»åè¡é·é· Aditya Raina 說ããæåç HBM3E 解決æ¹æ¡ä¸ä½ç¶éç½é©èï¼äº¦ééå¤åå

é²æè¡è主æµå» åçé©èï¼èæçºç²å¾å¤å®¶å¤§å» æ¡ç¨ï¼ä¹å½°é¡¯åºéå解決æ¹æ¡çç©©å¥åº¦èåªå¢ãæåæå¾

ç¹¼çºçºå種æç¨æä¾æ¯æï¼å

æ¬äººå·¥æºæ

§ãé«æè½éç®ã網路åæ±½è»ã

ç¾å

AI Solutions Groupç senior director Girish Cherussery 表示3è¨æ¶é«æ¯äººå·¥æºæ

§ä¼ºæå¨ä¸å¯æ缺çä¸é¨åï¼ä¹æ¯è³æä¸å¿ç³»çµ±æè½åé²æ¥çåºç¤ã”ãç¾å

åç´æä½³çè¨æ¶é«é度åè½æºæç表ç¾ï¼é常æçæ¼å æä¾å¦ ChatGPT ç大åèªè¨æ¨¡åéé¡çæå¼ AI å·¥ä½è² è¼æ¥çå¢å çéæ±ï¼é²èæ¯æ´ AI ç¶ææé·æ¥èª¿ãã

欲äºè§£æ´å¤è³è¨ï¼è«ç´æ¥è¯ç¹«æ¨çåµæé»åé·å®ä»£è¡¨ï¼è¯çµ¡è³è¨è«åè¦: https://www.guc-asic.com/en/about-offices.php

Related Semiconductor IP

Related News

- 西部数据通过收购喀山网络加速下一代数据中心架构的领军地位

- 用于超大规模数据中心芯片的112G Ethernet PHY重磅发布,支持800G网络应用

- Rambus发布面向增强型数据中心以及5G基础设施安全的完整800G MACsec解决方案

- Silex Insight推出1.5Tbps MACsec解决方案,助力5G基础架构