Dolphin Integration 延长电池供电SoC 2至5倍的操作时间

Grenoble, France – February 13, 2017 -- Allowing devices to run on the same battery for years rather than months partakes in enhancing significantly end-user satisfaction. Numerous wireless communication SoC, whether BLE, Zigbee, Sigfox, LoRa, M2M 4G…, have a duty cycle such that the power consumption in sleep mode dominates the overall current drawn from the battery. For such applications, the design of the “Always-On power domain" (a.k.a AON power domain) is critical.

To extend the operation time of such battery-operated SoC by x2 to x5, Dolphin Integration proposes, from 180 nm down to 40 nm, three innovative voltage regulators as part of its DELTA library.

Minimization of the power consumption of an always-on domain indeed involves paying special attention to the construct of the power regulation network. The selection of the voltage regulator is critical, as it may contribute to more than 50% of the power consumption in sleep mode. Furthermore, the capability of an always-on power domain to operate at very low voltage may significantly lower the power consumption while enabling silicon area and BoM cost savings.

The qLR-Aubrey is a linear regulator with a quiescent current as low as 150 nA, including the reference/bandgap. This innovative voltage regulator supports an input voltage as high as 5.5 V (no special process option required) and an output voltage programmable down to 0.55 V, i.e. the minimum data retention voltage of RAMs at 55 nm uLP. Embedding a single instantiation of the qLR-Aubrey to supply both the blocks in data retention and the always-on domain allows saving silicon area and BoM cost while reducing by up to 80% the power consumption of a SoC in sleep mode.

To make such savings achievable, Dolphin Integration provides a complete set of silicon IPs optimized to operate Near Threshold Voltage: standard cell library (SESAME NTV), ultra-low power XTAL and RC oscillators…

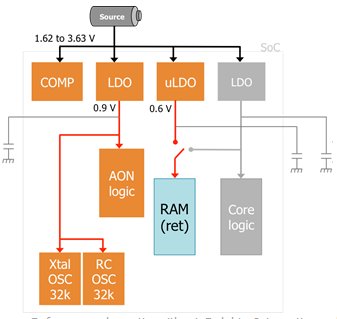

Reference schematic without Dolphin Integration solutions

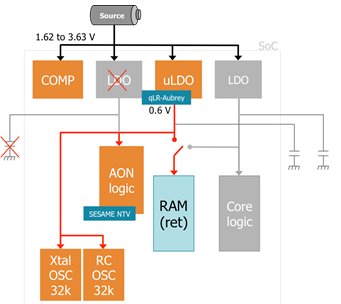

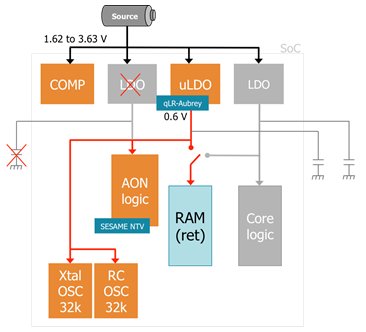

Always-on relying on Dolphin Integration Near Threshold Voltage solutions

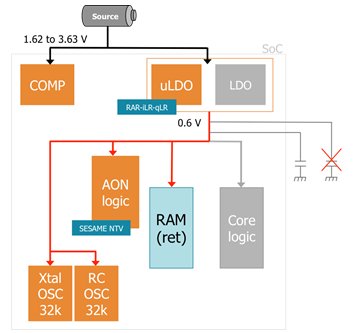

Dealing with multiple voltage regulators to supply the same load in different power modes is challenging (risks of short circuits…). Our unique RAR, i.e. Retention Alternating Regulator, is the solution. It combines two voltage regulators which operate alternatively: one during SoC active mode(s) – up to 1 A – and the other during SoC sleep mode(s) – up to 1 mA –. The switching between the two voltage regulators is fully automatic – activated through a control signal –, and is both fast and safe thanks to the Regulator Control Unit embedded in the RAR.

Depending on whether the target application of the SoC is more sensitive to BoM costs or to power consumption in active modes, SoC designers may select:

-

The RAR-iLR-qLR combines a fast transient linear regulator (iLR-Victoria) with an ultra-low quiescent regulator (qLR-Aubrey) for the lowest BoM cost.

-

The RAR-eSR-qLR combines a high-efficiency switching regulator (eSR-Niagara) with an ultra-low quiescent regulator (qLR-Aubrey) for the best power efficiency.

Schematic with qLR Aubrey and SESAME NTV

Schematic with RAR-eSR-iLR and SESAME NTV

| AON of reference | AON supplied with the qLR-Aubrey | AON supplied with a RAR-iLR-qLR | |

| Voltage regulators | 3 LDOs | 2 LDOs | 1 RAR |

| BoM cost | 3 capacitances | 2 capacitances | 1 capacitance |

Provided with integration rules, guidelines and specific views, voltage regulators of the DELTA library may be easily and safely embedded, whatever the complexity of the power regulation network and the sensitivity of loads to noise (e.g. RF).

Download our Datasheets on MyDolphin

Dolphin Integration will unveil its complete offering of innovative silicon IPs operating Near Threshold Voltage, and proven in the Taishan Demochip at TSMC 55 nm uLP/uLP eF, during the TSMC symposiums in Santa-Clara (USA) on March 15th and in Shanghai (China) on March 28th.

To get an overview ahead of these symposiums, you may discover our complete Always-On panoply.

About Dolphin Integration

Dolphin Integration contributes to "enabling low-power Systems-on-Chip" for worldwide customers - up to the major actors of the semiconductor industry - with high-density Silicon IP components best at low-power consumption.

"Foundation IPs" includes innovative libraries of standard cells, register files and memory generators as well as an ultra-low power cache controller. "Fabric IPs" of voltage regulators, Power Island Construction Kit and their control network MAESTRO enable to safely implement low-power SoCs with the smallest silicon area. They also star the "Feature IP": from ultra-low power Voice Activity Detector with high-resolution converters for audio and measurement applications to power-optimized 8 or 16 and 32 bit micro-controllers.

Over 30 years of experience in the integration of silicon IP components, providing services for ASIC/SoC design and fabrication with its own EDA solutions, make DOLPHIN Integration a genuine one-stop shop addressing all customers' needs for specific requests.

It is not just one more supplier of Technology, but the provider of the DOLPHIN Integration know-how!

Related Semiconductor IP

- SHA-256 Secure Hash Algorithm IP Core

- EdDSA Curve25519 signature generation engine

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

- LunaNet AFS LDPC Encoder and Decoder IP Core

Related News

- Intrinsic ID 与 Synopsys 合作提高 SoC 安全性并加快上市时间

- 全新Cadence Modus测试解决方案最高可将系统级芯片测试时间缩短三倍

- Cadence提供10个新的VIP解决方案,以加速基于关键新标准的市场应用时间

- Arteris公司宣布2016年有9个新的许可证持有者,多个互连IP产品发布和运营盈利状况