Andes晶心科技与 MachineWare 合作AndesCore® AX45MPV的仿真器供用户可早期开发RISC-V软件

德国亚琛与台湾新竹 — 2024年2月27日 — MachineWare GmbH与高效能低功耗32/64位RISC-V处理器核心领导供货商,同时也是RISC-V 国际协会创始首席会员的Andes晶心科技(TWSE:6533),共同宣布了一个令人振奋的新合作篇章,标志着战略合作伙伴关系的正式开始。这次合作针对的是极具创新性的AndesCore® AX45MPV,一款专为AI工作负载加速和应用层面设计的尖端多核RISC-V向量处理器。在此次合作中,MachineWare将 AX45MPV 无缝整合到其高效能模拟解决方案SIM-V中来并提供支持。事实证明,对于软件开发人员来说,这种解决方案能够有效地处理复杂的 AI 和 Linux 堆栈相关工作。在芯片试产之前,使用该虚拟平台就可以简化软件开发、测试和验证。这次合作凸显了MachineWare和Andes晶心科技在推动处理器技术进步方面的共同承诺。

SIM-V是MachineWare的一项产品,对于RISC-V领域的开发人员来说,具有极大的价值。借助SIM-V,开发人员可以在首批芯片从晶圆厂回来之前,就彻底测试和验证其基于RISC-V的系统和软件应用。SIM-V 的核心是提供支持所有 RISC-V 标准扩充的快速指令集仿真器 (ISS)。SIM-V的一大亮点是其方便使用的可自定义扩充性。透过简单的扩充SDK,开发人员可以快速整合自定义指令、寄存器和其他元素到仿真器中,以获得有关其设计选择的实时回馈。而使SIM-V真正与众不同的是其与SystemC TLM-2.0的整合。这一独特组合让用户能够将其IP模型无缝导入完整的系统仿真环境,提升平台的多功能性。

AX45MPV是一个64位8级流水线双发射多核心RISC-V处理器,包含RISC-V GCBP*(*P扩展指令集为草稿版本)扩展指令集功能,并支持具有内存管理单元

(MMU)的对称多处理(SMP) Linux,且最多可支持48位的虚拟地址。此外,它可以配置最多八个核心,并在一个cluster中配置带有缓存一致性管理器和最多8MB共享L2缓存的内存。AX45MPV的向量处理单元(VPU)实现了RISC-V向量扩展(RVV)1.0版本,支持最多1024位向量宽度(VLEN)和数据信道宽度(DLEN)的配置。AX45MPV在处理大数据数组计算方面表现卓越,适用于计算机视觉、数字信号处理、图像处理、机器/深度学习和科学计算等应用。

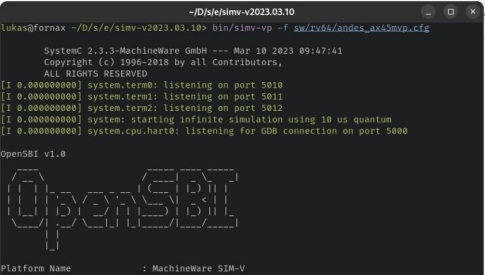

Figure 1: Invoking SIM-V with the AX45MPV configuration.

「我们非常高兴能与Andes晶心科技合作,在SIM-V中支持AX45MPV处理器。」MachineWare的总经理Lukas Jünger表示。「与AX45MPV模型的整合使我们的共同客户能够在短时间内开发RISC-V Linux和AI软件堆栈(software stacks)并验证其功能。这将降低错误并提升软件质量,同时加速整体开发过程。」

「Andes晶心科技与 MachineWare 的合作,展现了我们持续扩展 RISC-V 生态系统的决心,也就是让高效能模拟工具的采用更加便捷。」 Andes晶心科技市场处副处长姜新雨表示。「我们很高兴能与MachineWare携手推动RISC-V生态系统的扩展。我们相信RISC-V的指令集架构将促进创新,并有潜力改变人工智能市场。」

关于 MachineWare

MachineWare于2022年成立于德国亚琛,拥有数十年系统级仿真和高性能仿真工具的经验。详情请访问官方网站 https://www.machineware.de/ 。

关于Andes晶心科技

Andes晶心科技股份有限公司于2005年成立于新竹科学园区,2017年于台湾证交所上市 (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099)。晶心是RISC-V国际协会的创始首席会员,也是第一家推出商用RISC-V向量处理器的主流CPU供货商。为满足当今电子设备的严格要求,晶心提供可配置性高的32/64位高效能CPU核心,包含DSP、FPU、Vector、超纯量 (Superscalar)、乱序执行 (Out-of-Order)、多核心及车用系列,可应用于各式SoC与应用场景。晶心提供功能齐全的整合开发环境和全面的软/硬件解决方案,可帮助客户在短时间内创新其SoC设计。截至2023年底,Andes-Embedded™ SoC累计出货量已超过140亿颗。 更多关于Andes晶心的信息,请参阅晶心官网https://www.andestech.com 。订阅晶心微信公众号AndesTech及Bilibili获得最新消息!。

关于 RISC-V

RISC-V开放架构指令集架构由RISC-V International管理。详情请访问官方网站 https://riscv.org 。

Related Semiconductor IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- 64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

Related News

- Andes晶心科技隆重推出高性能 AndesCore® RISC-V 多核矢量处理器 AX45MPV

- Andes晶心科技、TASKING与MachineWare三方合作 推动RISC-V ASIL合规车用芯片快速开发

- Andes晶心科技推出 AndeSight® IDE v5.4,简化 RISC-V 上的 AI 与嵌入式软件开发

- Imperas模拟器支持Andes Custom Extension™ 加速特定领域应用软件开发