IPsec and TLS Engine IP

Welcome to the ultimate IPsec and TLS Engine IP hub! Explore our vast directory of IPsec and TLS Engine IP

All offers in

IPsec and TLS Engine IP

Filter

Compare

18

IPsec and TLS Engine IP

from

9

vendors

(1

-

10)

-

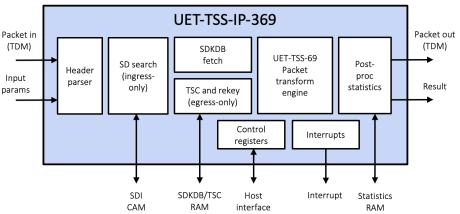

Multi-channel Ultra Ethernet TSS Complete Layer

- The UET-TSS-IP-369 (EIP-369) is an inline, high-performance, multi-channel packet engine that provides the complete TSS layer, bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

- The EIP-369 embeds the UET-TSS-IP-69 for the packet transformation.

-

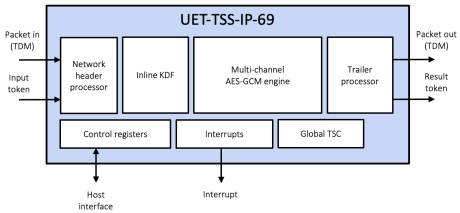

Multi-channel Ultra Ethernet TSS Transform Engine

- The UET-TSS-IP-69 (EIP-69) is a high-performance, multi-channel transform engine that provides the complete TSS packet transformation (including KDF and IP/UDP updates), bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

-

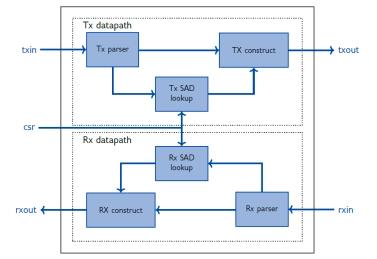

IPSEC AES-256-GCM (Standalone IPsec)

- XIP7213E implements the Internet Protocol Security (IPsec) as standardised in RFC4303 and RFC4305.

- The IPsec protocol defines a security infrastrucure for Layer 3 (as per the OSI model) traffic by assuring that a received packet has been sent by the transmitting station that claimed to send it.

-

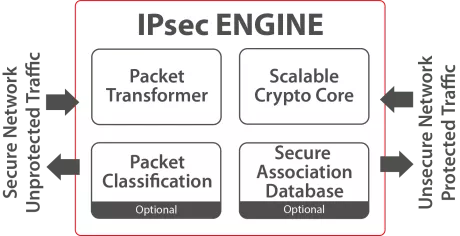

IPsec Engine

-

The IPsec Engine implements RFC4301 and other relevant RFCs, providing confidentiality, connectionless data integrity, data-origin authentication and replay protection on OSI layer 3.

-

-

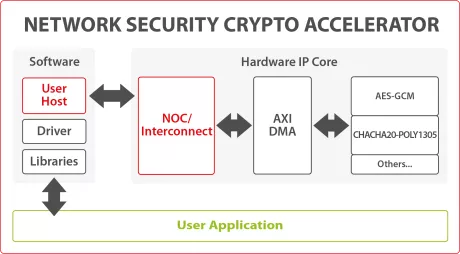

Network Security Crypto Accelerator

- The Network Security Crypto Accelerator is a hardware IP core platform that accelerates cryptographic operations in System-on-Chip (SoC) environment on FPGA or ASIC.

- This IP is used to accelerate/offload MACsec, IPsec, VPN, TLS/SSL, disk encryption, or any other custom application, requiring symmetric cryptography algorithms.

-

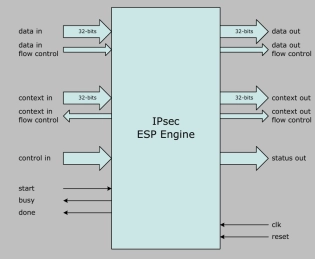

IPsec ESP IP core for FPGA

- Built on the success of Helion's industry proven cryptographic IP cores, the Helion ESP Engine provides hardware acceleration of the key cryptographic algorithms and packet processing required by the IPsec Encapsulating Security Payload (ESP) protocol.

- Its modular architecture provides the flexibility to support only those cryptographic algorithms required for a particular application to provide the optimum logic area and performance trade-off.

-

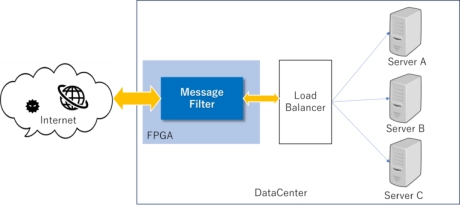

Message filter

- Message filters are placed in the middle of a TCP / TLS session to scan application data, and discard unwanted messages and security-issue packets, reducing unnecessary traffic without increasing CPU load or latency.

- Unlike filters by IP address or port, which scan the data content and discard or pass through packets, DPI (Deep Packet Inspection) and other methods tend to cause CPU processing load and packet processing delays.

-

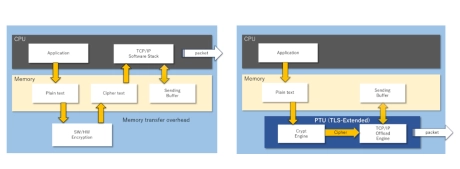

SSL/TLS Offload Engine

- Our SSL/TLS engine accelerates and offloads processing for encryption / decryption and authentication in SSL / TLS by combining our TCP offload and crypt engine.

- Since the record layer processing is completely hardware offloaded, the user application can overwhelmingly reduce the CPU load which only needs preparing the data to transfer securely.

-

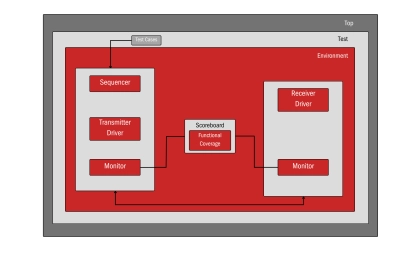

TLS - Validates TLS protocols to ensure secure, encrypted data transmission

- TLS Verification IP (VIP) ensures secure communication by validating TLS protocol implementations. It simulates handshake processes, tests encryption, and verifies data integrity to protect against cyber threats during data transmission.

- This product finds application in web browsing, email security, VPNs, cloud services, mobile apps, and more. It safeguards sensitive data across various platforms, ensuring end-to-end encryption and robust protection in diverse network environments

-

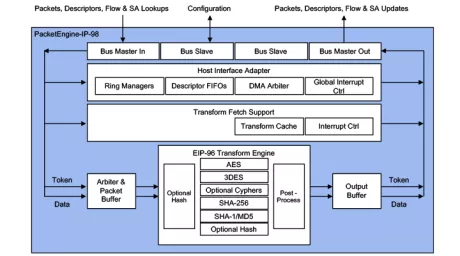

Multi-Protocol Engine with Classifier, Look-Aside, 5-10 Gbps

- Protocol aware IPsec, SSL, TLS, DTLS, 3GPP and MACsec Packet Engine with virtualization, caches classifier and Look-Aside interface for multi-core application processors

- 5-10 Gbps, programmable, maximum CPU offload by classifier, supports new and legacy crypto algorithms, AMBA interface

- Supported by Driver development kit, QuickSec IPsec toolkit, Linaro ODP, DPDK, Linux Crypto