secure connection engine IP

Filter

Compare

7

IP

from

7

vendors

(1

-

7)

-

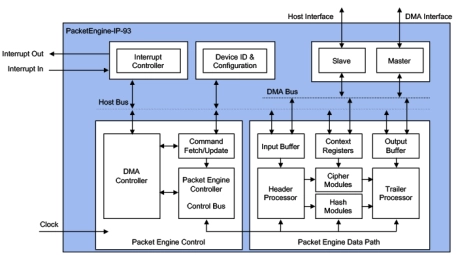

Multi-Protocol Engine, Look-Aside, 1 Gbps

- Protocol-aware IPsec/TLS packet engine with Look-Aside interface for IoT.

- Up to 1 Gbps, lowest gate count in the industry, just 100K gates (ex AMBA interface).

- Supported by Driver Development Kit, QuickSec IPsec toolkit, Secure Boot Toolkit.

-

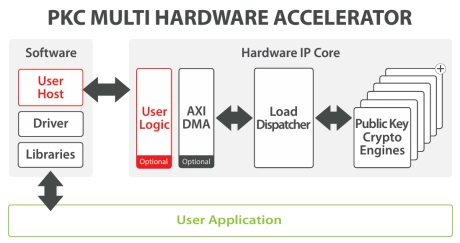

PKC Multi Hardware Accelerator IP

- The PKC Multi hardware accelerator is a secure connection engine that can be used to offload the compute intensive Public Key operations (Diffie-Hellman Key Exchange, Signature Generation and Verification), widely used for High-performance TLS Handshake.

-

IPsec Security Processor

- Support for IPv4 and IPv6 packets

- Support for the IPsec ESP and AH protocols:

- Support for IPsec ESP encryption algorithms per RFC 4835:

- Support for IPsec ESP (and AH for –AH option) authentication algorithms per RFC 4835:

-

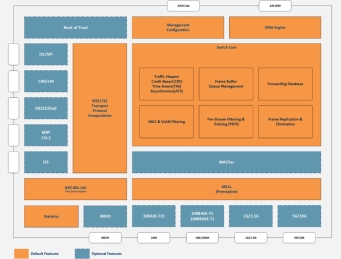

Zonal Controller

- Complete solution that integrates both hardware and software components including a TSN-capable Ethernet switch, a Root of Trust security module, and a transport protocol encapsulation system based on IEEE 1722

-

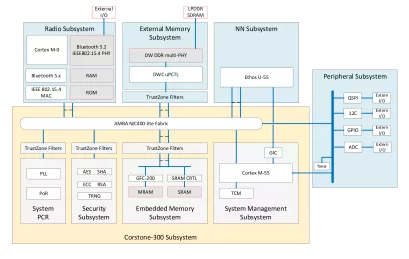

IP platform for intelligence gathering chips at the Edge

- High performance IoT solutions for AI at the Edge can now be created up to 30% faster

-

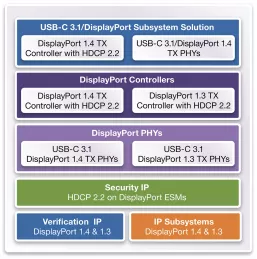

USB-C 3.1/DisplayPort 1.4 IP Subsystem Solution

- Built from USB-IF certified DesignWare USB 3.1 solution

- Built from VESA certified DesignWare DisplayPort 1.4 Tx solution

- Single delivery with a single top-level view of subsystem

- Industry’s only USB Type-C IP solution consisting of USB-C 3.1/DisplayPort 1.4 TX PHYs, USB-C 3.1/DisplayPort 1.4 TX controllers with HDCP 2.2 and HDCP 1.4 content protection, verification IP, and IP subsystems

-

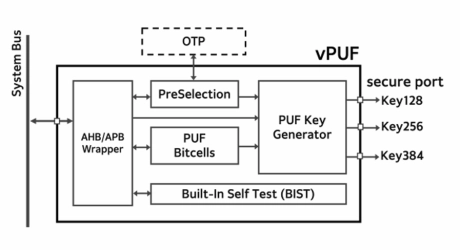

Via-PUF Security Chip for Root of Trust

-

The vPUF® IP, powered by Via PUF (Physically Unclonable Function) technology, provides a unique silicon fingerprint for inborn identity function, essential for the Root of Trust in security applications

-