motor control IP

Filter

Compare

19

IP

from

11

vendors

(1

-

10)

-

Real-Time Microcontroller - Ultra-low latency control loops for real-time computing

- Reliable event driven computing is enabled by the unique MIPS M8500 real-time multithreaded architecture.

- The M8500 is an easy-to-use general-purpose microcontroller with advanced efficiency and performance for sub -10μs control loop algorithms.

- The M8500 is a turnkey closed loop control solution with functional safety options and end-to-end software solution.

-

CORDIC Algorithm Accelerator

- 24-bit CORDIC rotation engine

- Circular and Hyperbolic modes

- Rotation and Vectoring modes

- Functions: sine, cosine, sinh, cosh, atan, atan2, atanh, modulus, square root, natural logarithm, exp

-

Tensilica FloatingPoint KQ7/KQ8 DSPs

- VLIW parallelism issuing multiple concurrent operations per cycle

- 512-bit and 1024-bit SIMD

- IEEE 754 vector floating-point (HP, SP, DP)

- Performance-optimized fused multiply-add (FMA)

-

Tensilica FloatingPoint KP1/KP6 DSPs

- VLIW parallelism issuing multiple concurrent operations per cycle

- Xtensa LX Secure Mode

- 128-bit and 512-bit SIMD

- IEEE 754 vector floating-point

-

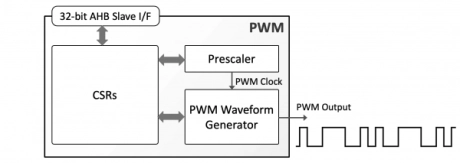

Pulse Width Modulator

- The PWM IP core implements a compact and highly flexible Pulse Width Modulator. The core generates a repeated pattern of pulse trains of run-time configurable period and duty cycle.

- Those pulse trains can be used in a wide variety of applications including but not limited to motor control and LED dimming. They can also be filtered with a lowpass filter to implement Digital to Analog Converters (DAC).

-

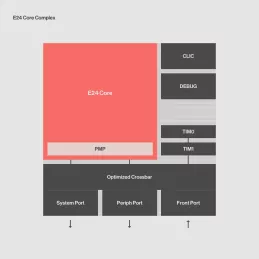

E34 Standard RISC V Core

- Fully compliant with the RISC-V ISA specification

- RV32IMAFC Support

- RV32I - 32-bit RISC-V with 32 integer registers

- Integer Multiplication and Division (M) support

-

E24 High-performance microcontroller with hardware support

- RISC-V ISA - RV32IMAFC

- Machine and User Mode with 4 Region Physical Memory Protection

- 3-stage pipeline with Simultaneous Instruction and Data Access

- 2 Banks of Tightly Integrated Memory

-

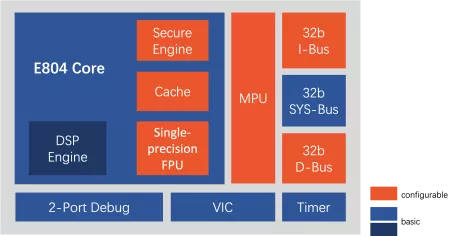

Low power 32-bit processor with lightweight computing power

- Instruction set: T-Head ISA (32-bit/16-bit variable-length instruction set);

- Pipeline: 3 to 4-stage variable length pipeline;

- General register: 32 32-bit GPRs;

- Bus interface: Tri-bus (instruction bus + data bus + system bus);

-

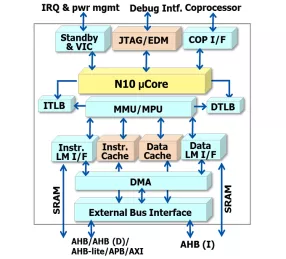

Full-featured Real-time Application Processor

- Caches for fast code and data accesses

- Local Memories for deterministic code and data accesses

- IEEE754-compliant FPU coprocessor

- Memory Protection Unit (MPU) for secure RTOS