eMMC PHY IP

Filter

Compare

59

IP

from

11

vendors

(1

-

10)

-

EMMC PHY & Controller

- Dolphin Technology delivers custom, synthesizable IP to support specific design requirements.

- The DTI EMMC controller provides the logic to integrate a Host and PHY controller supporting embedded MultiMediaCard (eMMC) version 5.1 into any system on chip (SoC).

-

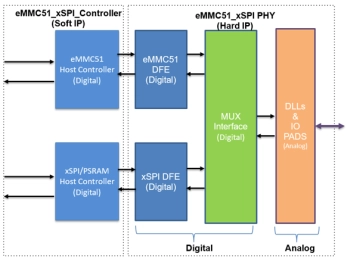

xSPI + eMMC Combo PHY IP

- This IP integrates both xSPI (Expanded Serial Peripheral Interface) and eMMC 5.1 PHY (Physical Layer) into a single unified solution, enabling support for two distinct memory protocols within the same IP.

- By combining the PHY layers for both interfaces, the design simplifies system integration, reduces area and pin count, and enhances design flexibility for SoCs that require both boot and high-speed storage functionality.

-

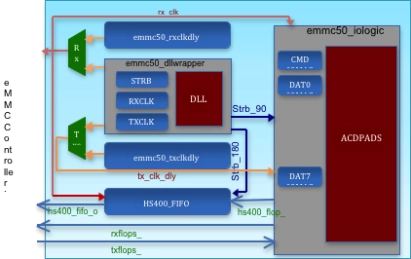

eMMC 5.1 HS400 PHY

- The eMMC5.1 PHY is a fully compliant PHY layer for JEDEC eMMC5.1 and eMMC5.1 JESD84-B50 specification. It is backward compatible with eMMC4.51 and earlier versions of the specifications.

- This allows the designers of the SoC to easily support the eMMC interface and optimize the performance and power while maintaining interoperability with eMMC 5.0 and eMMC 5.1 devices.

-

TSMC N5A SD/eMMC PHY AG2 Platform

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC N3P SD/eMMC PHY North/South Poly Orientation MS add-on

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC N3P SD/eMMC PHY North/South Poly Orientation

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC N3E SD/eMMC PHY North/South Poly Orientation

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC N3A SD/eMMC PHY AG2 North/South Poly Orientation

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

Samsung 8LPU 1.8V/3.3V SD/eMMC PHY AP1

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

Samsung 5LPE 1.8V/3.3V SD/eMMC PHY AP2

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards