Vision Processor IP

Filter

Compare

57

IP

from

17

vendors

(1

-

10)

-

-

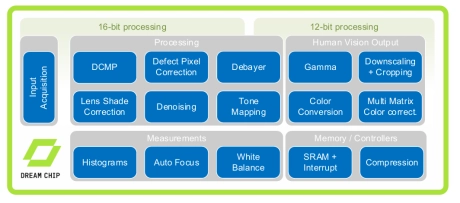

Real-time Pixel Processor for Vision applications

- The W Series provides configurable input and output data widths.

- It supports input image frames with 8 to 16-bit amplitude resolutions, while it can output tone-mapped frames with 12 bits per pixel.

- The W Series are ISPs which are optimized for area while getting the best image quality.

-

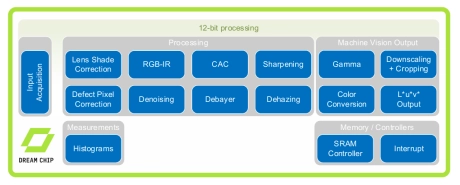

Real-time Pixel Processor for Vision applications

- The H Series provides configurable input and output data widths. It accepts YCbCr or RAW input data and supports input image frames with 8, 10 and 12-bit amplitude resolutions.

- The H1 Series are ISPs which are optimized for area while getting the best image quality.

- Options to extend the pipeline with a Machine Vision output or configuring the line size to further optimize area are possible.

-

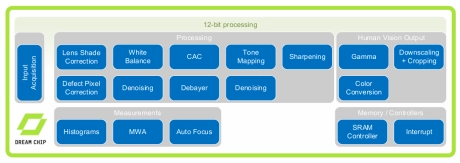

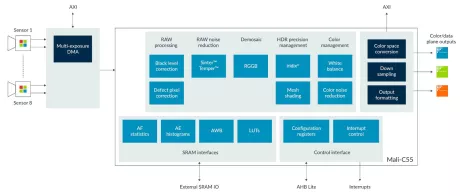

Image signal processor to advance vision systems for IoT and embedded markets

- Multi-sensor interface with up to 20-bit linear video input

- Up to 8 independent camera sources of max resolution 48 Megapixels / 8K (8192 x 6144)

-

ARC EV Processors are fully programmable and configurable IP cores that are optimized for embedded vision applications

- ARC processor cores are optimized to deliver the best performance/power/area (PPA) efficiency in the industry for embedded SoCs. Designed from the start for power-sensitive embedded applications, ARC processors implement a Harvard architecture for higher performance through simultaneous instruction and data memory access, and a high-speed scalar pipeline for maximum power efficiency. The 32-bit RISC engine offers a mixed 16-bit/32-bit instruction set for greater code density in embedded systems.

- ARC's high degree of configurability and instruction set architecture (ISA) extensibility contribute to its best-in-class PPA efficiency. Designers have the ability to add or omit hardware features to optimize the core's PPA for their target application - no wasted gates. ARC users also have the ability to add their own custom instructions and hardware accelerators to the core, as well as tightly couple memory and peripherals, enabling dramatic improvements in performance and power-efficiency at both the processor and system levels.

- Complete and proven commercial and open source tool chains, optimized for ARC processors, give SoC designers the development environment they need to efficiently develop ARC-based systems that meet all of their PPA targets.

-

Safety Enhanced GPNPU Processor IP

- A True SDV Solution

- Fully programmable – ideal for long product life cycles

- Scalable multicore solutions up to 864 TOPS

- Solutions for ADAS, IVI and ECU products

-

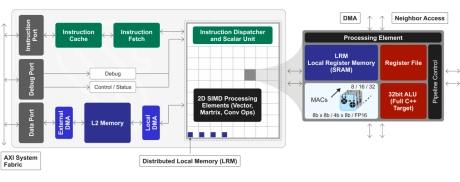

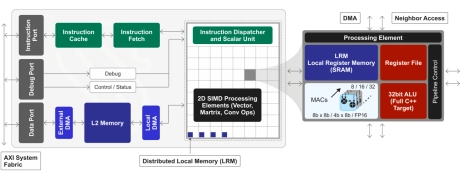

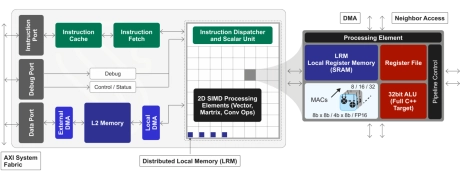

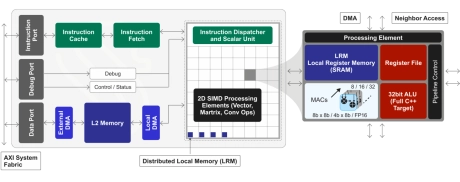

GPNPU Processor IP - 32 to 864TOPs

- 32 to 864TOPs

- (Dual, Quad, Octo Core) Up to 256K MACs

- Hybrid Von Neuman + 2D SIMD matrix architecture

- 64b Instruction word, single instruction issue per clock

- 7-stage, in-order pipeline

- Scalar / vector / matrix instructions modelessly intermixed with granular predication

-

-

-