Video Pipeline IP

Filter

Compare

66

IP

from

21

vendors

(1

-

10)

-

Pipelined AES G3 for Video

- Low area, pipelined implementation of AES with moderate key latency suitable for video encryption/decryption.

- Based on the NIST validated (Cert #953) AES-G3 implementation of the Advanced Encryption Standard

- Supports 128, 192 and 256 bit keys

- Targets all modern FPGA families from Xilinx, Altera, Lattice and Microsemi

-

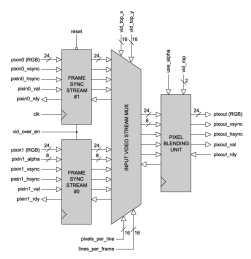

Digital Video Overlay Module

- The TXT_OVERLAY IP Core is a highly versatile On Screen Display (OSD) module that allows text and bitmap graphics to be inserted over RGB video.

- The module supports a wide range of text effects and the programming interface is very simple.

- Text is written to a character buffer which is mapped (via a bitmap ROM) directly to the display.

-

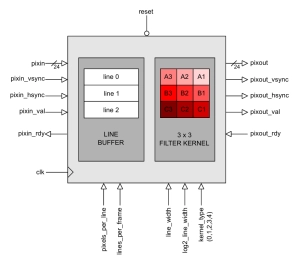

Digital Video Anti-aliasing filter IP Core

- The ALIAS_FILTER IP Core is a fully pipelined anti-aliasing filter for use in digital video applications.

- The design implements a low pass filter response on the source video in order to alleviate problems such as jagged edges, stepped lines and Moiré interference patterns.

- This is especially important when downscaling and upscaling video by large factors.

-

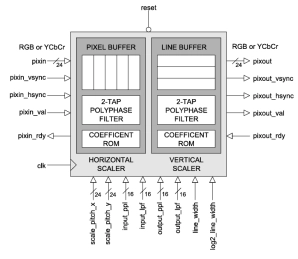

Bilinear Video Scaling Engine

- XY2_SCALER is a very high quality video scaler capable of generating interpolated output images from 16x16 up to 216 x 216 pixels in resolution.

- The architecture permits seamless scaling (either up or down) depending on the chosen scale factor.

- Internally, the scaler uses a 24-bit accumulator and a bank of polyphase FIR filters with 16 phases or interpolation points.

- All filter coefficients are programmable, allowing the user to define a wide range of filter characteristics.

-

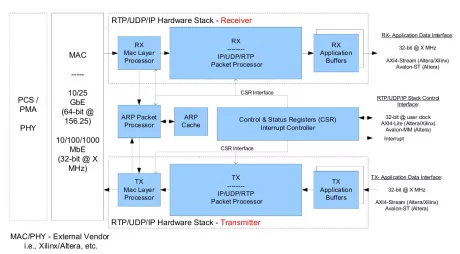

RTP/UDP/IP Protocol Hardware Stack – H.264/H.265 NAL Video Streams Packet Processing

- RTP/UDP/IP Protocol Hardware Stack, targets H.264 NAL Streams. See DB RTP-UDP-IP-AV for raw, uncompressed RGB/YUV video streams

- For RX (i.e., receiving packets from the network), there is optional packet reordering to absorb network jitter.

- For both TX/RX, multiple NAL video streams supported. The DB-RTP-UDP-IP-NAL targets H.264 NAL Streams.

-

4K Video Scaler IP Core

- Technology independent soft IP Core for FPGA, SoC and ASIC devices

- Supplied as human readable VHDL source code (or Verilog on request)

- Versatile RGB video scaler capable of scaling up or down by any factor

- Fully programmable scale parameters and scaler bypass function

-

64 bit Video / Image DSP

- Custom Matrix instruction support

- Tightly-coupled vector unit

- 3-issue / Out-of-order / 8-stage scalar pipeline

- Full Linux OS support

-

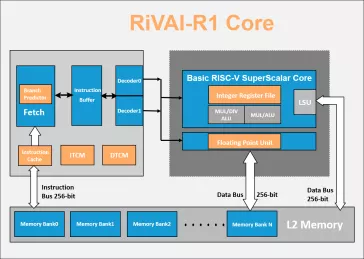

High performance dual-issue, out-of-order, 7-stage pipeline superscalar core

- Design Flexibility

- Portability

- Ease of programmability

-

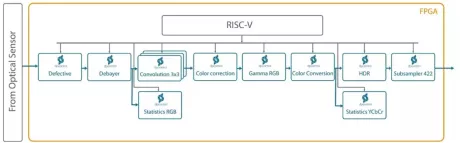

Image Signal Processing Pipeline IP core

- Extremely flexible and versatile, ISPIDO can be tailored on ultra low powered battery operated devices, up to higher than 8K resolution vision systems.

- Each module of the image Signal Processing Pipeline, proposed by DPControl, has been implemented respecting the compatibility with the AMBA AXI4 standards, making the entire architecture completely configurable and versatile.

- The ISP accepts in input a video stream with 8 or 10 or 12 bits depth. The Defective Correction module takes care of eliminating the Salt-Pepper error.

-

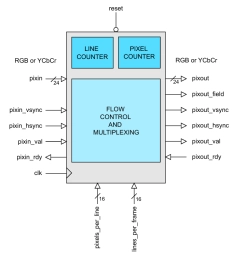

Video Interlacer

- The INTERLACER IP Core is a fully pipelined video interlacer solution that converts any progressive video format into its interlaced equivalent.

- The format of the input video is defined by the parameters pixels_per_line and lines_per_frame.

- These values specify the size of one input frame of video in pixels and lines. Each interlaced output field will have half the number of lines as an input frame.