Video Controller IP

Filter

Compare

251

IP

from

38

vendors

(1

-

10)

-

Compact Multilayer Video Controller

- Display controller IP core for LCD displays

- Supports Xilinx Zynq-7000 AP SoC and all Xilinx FPGA

- 64x1 to 2048x2048 display resolutions; higher resolutions support available on request

- Supports up to 5 layers

-

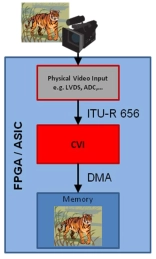

Customizable Video Input controller

- CVI is a fully Customizable Video Input controller IP core.

- The video input controller can be applied to e.g. FPGA systems with a resource optimized, application specific feature configuration or to ASIC projects applying a more generic feature set and thus more flexibility.

-

Video Timing Controller

- Automatic detection of horizontal and vertical blanking, synchronization pulses and active video

- Optional AXI4-Lite interface allows processor systems to read the incoming video format and propagate configurations to downstream video processing blocks or program the video format for output timing generation

- Supports multiple combinations of horizontal and vertical video timing signal detection and generation

- Full Interrupt support for system event control

-

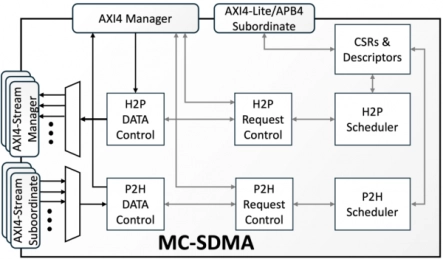

Multi-Channel Streaming DMA Controller

- The MC-SDMA IP core implements a highly configurable, bandwidth-efficient, and easy-to-use Direct Memory Access (DMA) controller that transfers data between the host system’s memory and multiple peripherals equipped with streaming interfaces.

- The core interfaces with the host memory via a manager AMBA® AXI4 (memory-mapped) port and provides access to its configuration and status registers (CSRs) via a subordinate AXI4-Lite or APB4 interface.

-

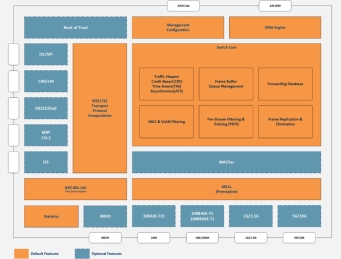

Zonal Controller

- Complete solution that integrates both hardware and software components including a TSN-capable Ethernet switch, a Root of Trust security module, and a transport protocol encapsulation system based on IEEE 1722

-

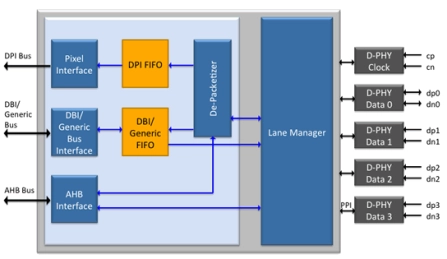

DSI Receiver Controller

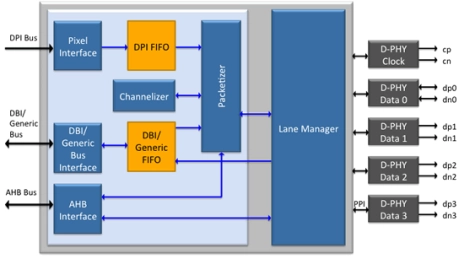

- The DSI v1.3 Receiver Controller IP is designed to provide MIPI DSI 1.3 compliant high-speed serial connectivity for device (mobile display modules) with Type 1 to 4 architectures.

- Serial connectivity to the mobile applications processor’s DSI host is implemented using 1 to 4 D-PHY’s (also available from Arasan), depending on display bandwidth needs.

-

MIPI DSI-2 Transmitter Controller IP Core

- The MIPI Display Serial Interface (DSI-2) Transmitter (host processor interface) Controller IP provides a high-speed serial interface between an application processor and display modules using either MIPI C-PHY v1.1 or MIPI D-PHY v1.2 and v2.0.

-

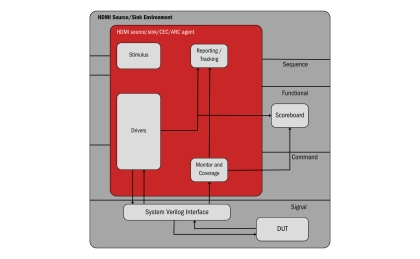

HDMI - Ensures seamless video and audio transmission with HDMI standards

- HDMI Verification IP validates HDMI controller functionality in SoC designs, ensuring compliance with HDMI standards like 1.4, 2.0, and 2.1. It verifies video/audio signal transmission, encryption, and data integrity for smooth multimedia experience.

- The VIP also tests advanced features like 3D video, HDR, and deep color formats, ensuring compatibility across various devices. It simulates scenarios like hot-plug detection and HDCP for secure, error-free content transmission in diverse real-world applications.

-

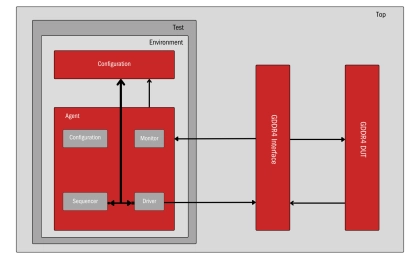

GDDR4 Controller - Validates high-speed memory controllers for efficiency and reliability

- The GDDR4 Controller Verification IP (VIP) ensures robust simulation and validation of GDDR4 memory controllers in SoC designs. Supporting high-speed data transfers, protocol compliance, and power management, it simplifies testing and optimizes system performance.

- Ideal for high-performance applications, GDDR4 VIP enhances GPU, HPC, gaming consoles, and embedded systems. Its broad use spans automotive, AI, video processing, networking, and consumer electronics, ensuring efficient memory operations across industries

-

Motorola MC6845 Functional Equivalent CRT Controller

- The DB6845 CRT Controller core is a full function equivalent to the Motorola MC6845 device.

- The DB6845 interfaces a microprocessor to a raster-scan CRT display. The microprocessor access 19 registers (1 Address and 18 Data Registers) within the DB6845 in order to provide video timing, refresh memory addresses, cursor, and light pen strobe signals.

- CRT video timing signals include Vertical Sync (VS), Horizontal Sync (HS), and Display Enable (DE) output signals. Refresh memory addressing includes Memory Address (MA[13:0]) and Row Address (RA[4:0]) output buses.