TSMC 12FFC IP

Filter

Compare

115

IP

from

7

vendors

(1

-

10)

-

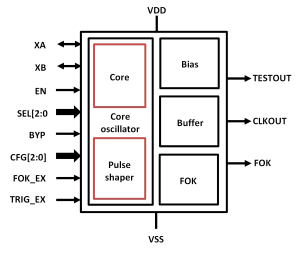

Ultra low-power crystal-based 32 kHz oscillator in TSMC 12FFC+

- OSC-XT-32k-T12FFC.01_TSMC_12_FFC+ is an ultra-low power crystal-based oscillator in TSMC 12FFC+ for accurate 32 kHz clock generation in the SoC Always-On domain (eg. implementation of RTC features).

- An embedded auxiliary loop controls the voltage amplitude at the crystal terminals for maximizing the power efficiency for multiple crystals.

-

24-bit Cap-less ADC with 101 dB SNR, offering low power consumption and low latency, supporting 1 channel (mono) in TSMC 12FFC+

- mADC101-SW3-FF.01 is a mixed-signal (analog and digital) virtual component in TSMC 12FFC+ that includes a single mono ADCs and additional functions, making it an ideal front-end for low power, fast wake-up, and high-quality audio applications.

- It also features ultra-low latency capability for ANC applications.

-

512x8 Bits OTP (One-Time Programmable) IP, TSMC 12FFC 0.8V/1.8V Process

- Fully compatible with TSMC 12FFC 0.8V/1.8V

- Low voltage: 0.8 V ± 10% for read and 1.1 V ± 5% for program

- High speed: 10µs program time per bit, and 50ns read 8-bit at a time

-

DDR4/ LPDDR4/ DDR3L PHY IP - 3200Mbps (Silicon Proven in TSMC 12FFC)

- Supported DRAM type: DDR3L/DDR4/LPDDR4

- Maximum controller clock frequency of 400MHz resulting in maximum DRAM data rate of 1866Mbps

- Interface: SSTL135/POD12/LVSTL

- Data path width scales in 32-bit increment

-

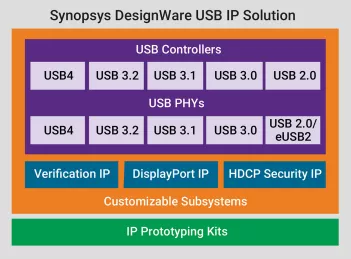

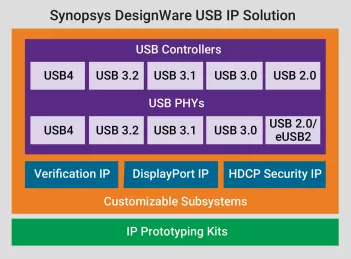

USB-C 3.1 SS/SSP PHY, Type-C - TSMC 12FFC, North/South Poly Orientation

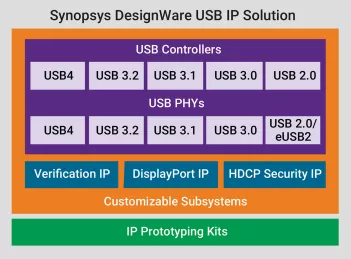

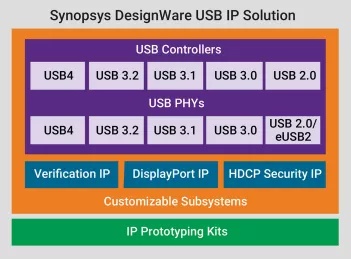

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB 3.1 PHY (10G/5G) - TSMC 12FFC x1 OTG, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB-C 3.0 femtoPHY, Type-C - TSMC 12FFC, North/South Poly Orientation

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification

-

USB 3.0 femtoPHY - TSMC 12FFC x1 OTG, North/South Poly Orientation

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification

-

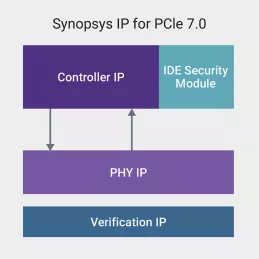

PCIe 4.0 PHY, TSMC 12FFC x4, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver

-

PCIe 4.0 PHY, TSMC 12FFC x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver