Synopsys Memory IP

Filter

Compare

361

IP

from

6

vendors

(1

-

10)

-

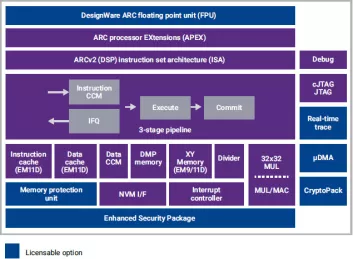

ARC EM9D 32-bit DSP Enhanced Processor core based on the ARCv2DSP ISA with CCM and XY Memory

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

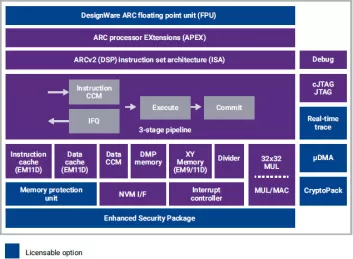

ARC EM11D Enhanced 32-bit processor core, ARCv2DSP ISA with Cache and XY Memory

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

Inline Memory Encryption (IME) Security Module - for DDR/LPDDR

- Data confidentiality with independent cryptographic support for read & write channels

- Standards compliant: NIST SP800-38E, IEEE Std. 1619-2018

- FIPS 140-3 certification support

- Per region protection (index or address based)

-

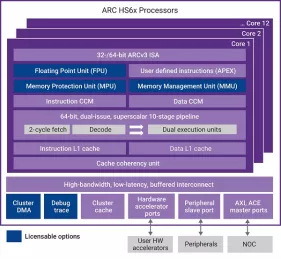

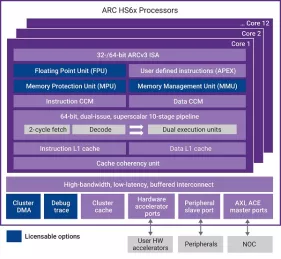

Memory management unit (MMU) option for ARC HS5x and HS6x processors

- Dual-issue, 64-bit processors for high-performance embedded applications

- 52-bit physical and 64-bit virtual addressing

- Up to 5400 DMIPS and 11,088 CoreMark per core at 1.8 GHz on 16FFC (worst case conditions, single-core configuration

- Multicore Processor versions with up to 12 CPU cores and up to 16 hardware accelerators

-

L2 cache/cluster shared memory option for multicore versions of ARC HS5x and HS6x processors

- Dual-issue, 64-bit processors for high-performance embedded applications

- 52-bit physical and 64-bit virtual addressing

- Up to 5400 DMIPS and 11,088 CoreMark per core at 1.8 GHz on 16FFC (worst case conditions, single-core configuration

- Multicore Processor versions with up to 12 CPU cores and up to 16 hardware accelerators

-

Performance Enhanced version of DDR Enhanced Memory Ctl (uMCTL2) supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3, and LPDDR2

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

LPDDR6/5X/5 PHY V2 - TSMC N6

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

LPDDR6/5X/5 PHY V2 - TSMC N5A for Automotive, ASIL B Random, AEC-Q100 Grade 2

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

LPDDR6/5X/5 PHY V2 - TSMC N5

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

LPDDR6/5X/5 PHY V2 - TSMC N4P

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications