SerDes PHY IP

Filter

Compare

223

IP

from

40

vendors

(1

-

10)

-

32Gbps SerDes PHY in GF 22nm

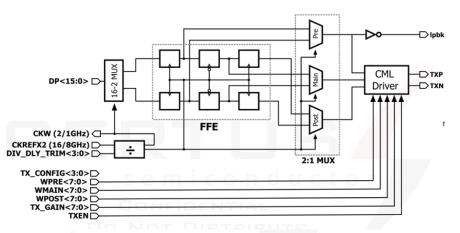

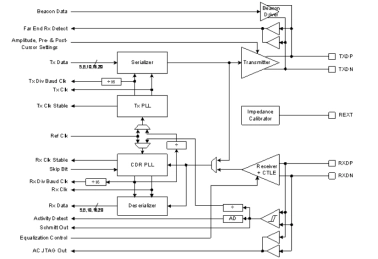

- This 32Gbps SerDes PHY is implemented in GlobalFoundries 22FDX CMOS technology and provides a high-performance, protocol-agnostic serial interface for advanced mixed-signal and high-speed digital SoCs.

- The PHY is architected as a modular design consisting of a low-jitter clock multiplier, a half-rate transmitter with digitally programmable feed-forward equalization, and a configurable CTLE-based receiver with digital clock-and-data recovery, supporting both 16 Gbps and 32 Gbps operation.

-

Programmable PCIe2/SATA3 SERDES PHY on TSMC CLN28HPC

- Programmable SERDES analog front end that supports 1 to 6+ Gbps standard serial protocols

- Compact form factor – 0.116 mm2 active silicon area per lane including ESD

- Industry leading low power – typically 6.3 mW/Gbps (@6Gbps) including termination

- Minimal latency – 3 UI between parallel transfer and serial transmission

-

PCI Express Gen5 SERDES PHY on Samsung 8LPP

- Industry leading low power PMA macro – 224mW per lane at 28Gbps (8.0 mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.38 mm2 active silicon area per lane including ESD

- Minimal latency – 3 UI between parallel transfer and serial transmission

- Single-lane macro scalable to unlimited link width – x1, x2, x4, x8, x16, etc.

-

PCI Express Gen4 SERDES PHY on Samsung 7LPP

- Industry leading low power PMA macro – 132.7mW per lane at 16Gbps (8.4mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.32 mm2 active silicon area per lane including ESD

- Minimal latency – 3 UI between parallel transfer and serial transmission

- Single-lane macro scalable to unlimited link width – x1, x2, x4, x8, x16, etc.

-

PCI Express Gen3/Enterprise Class SERDES PHY on Samsung 28LPP

- Industry leading low power PMA macro – 88mW per lane at 8Gbps (11.0 mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.216 mm2 active silicon area per lane including ESD

- Enterprise class Long Reach 5-tap DFE supporting beyond standard PCIe Channels

- Minimal latency – 3 UI between parallel transfer and serial transmission

-

PCI Express Gen3/4 Enterprise Class SERDES PHY on Samsung 14LPP

- Industry leading low power PMA macro – 132.7mW per lane at 16Gbps (8.4mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.266 mm2 active silicon area per lane including ESD

- Enterprise class Long Reach 5-tap DFE supporting beyond standard PCIe Channels

- Minimal latency – 3 UI between parallel transfer and serial transmission

-

PCI Express Gen3 SERDES PHY on TSMC CLN40G

- Programmable SERDES analog front end that supports 1 to 8 Gbps standard serial protocols

- Compact form factor – 0.107 mm2 active silicon area per lane including ESD

- Industry leading low power – typically 6.9 mW/Gbps including termination

- Minimal latency – 3 UI between parallel transfer and serial transmission

-

PCI Express Gen3 SERDES PHY on Samsung 7LPP

- Industry leading low power PMA macro – 36mW per lane at 8Gbps (4.5mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.1 mm2 active silicon area per lane including ESD

- Minimal latency – 3 UI between parallel transfer and serial transmission

- Single-lane macro scalable to unlimited link width – x1, x2, x4, x8, x16, etc.

-

PCI Express Gen3 SERDES PHY on Samsung 28LPP

- Programmable SERDES analog front end that supports 1 to 8 Gbps standard serial protocols

- Compact form factor – 0.134 mm2 active silicon area per lane including ESD

- Industry leading low power – typically 7.0 mW/Gbps including termination

- Minimal latency – 3 UI between parallel transfer and serial transmission

-

PCI Express Gen3 / SATA3 SERDES PHY on Samsung 28FDSOI

- Programmable SERDES analog front end that supports 1 to 8 Gbps standard serial protocols

- Compact form factor – 0.165 mm2 active silicon area per lane including ESD

- Industry leading low power – typically 6.5 mW/Gbps including termination

- Finely configurable receiver impedance, CTLE gain and bandwidth, with fully adaptive CTLE and DFE